在高速数字系统中,传输线上阻抗不匹配会引起信号反射,减小和消除反射的方法是根据传输线的特性阻抗在其发送端或接收端进行终端阻抗

2019-08-14 09:18

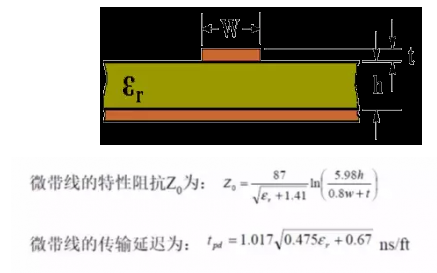

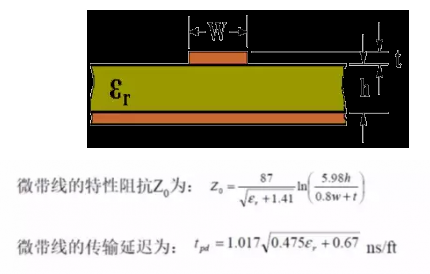

在设计高速 PCB 电路时,阻抗匹配是设计的要素之一。而阻抗值跟走线方式有绝对的关系,例如是走在表面层(microstrip)或内层(stripline/double

2018-07-03 19:10

随着现代电子电路信号传输速度的提高,对PCB品质性能的要求也越来越高。PCB提供的电路性能只有起到阻抗匹配,才能使信号在高速传输中保持稳定、无反射、信号完整、无杂讯失真

2022-12-12 14:04

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的

2017-11-26 14:28

在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时

2020-11-12 17:09

阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的

2019-09-06 11:52

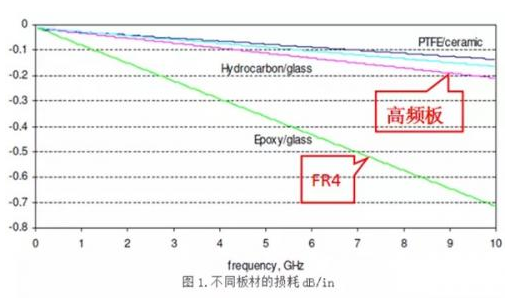

。保持数字信号的完整性以及上下沿的陡峭程度和射频微波(数字信号的高频谐波部分达到了微波频段)的低 损耗低失真传输一样。因此,在诸多方面,高速数字电路

2019-09-17 11:50

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2018-10-14 09:28

高速讯号会导致PCB板上的长互连走线产生传输线效应,它使得PCB设计者必须考虑传输线的延迟和阻抗搭配问题,因为接收端和驱动端的阻

2018-05-22 07:18