原理可理解为:单片机一上电的瞬间,电容相当于短路,所以5V电压全部集中在4.7K电阻上,然后,电容开始充电,当充电到一定时候,5V电压基本都集中在电容上了,电阻上的电压低于单片机需要的高电平电压。

2018-07-15 10:36

COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0,扇出数为10--20个COMS门电路。

2017-08-26 10:02

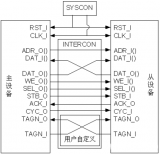

LOCK_O/LOCK_I:在操作过程中,仲裁器可能会提前将总线占用权收回并分配给其他主设备从而打断当前主设备的操作,LOCK_O/LOCK_I有效代表本次总线操作是不可打断的。仲裁器收到LOCK_I信号,就不会提前收回总线使用权,知道当前主机将该信号拉低。图5中只有一个主设备和一个从设备,因此没画出仲裁器模块。

2018-07-10 08:26

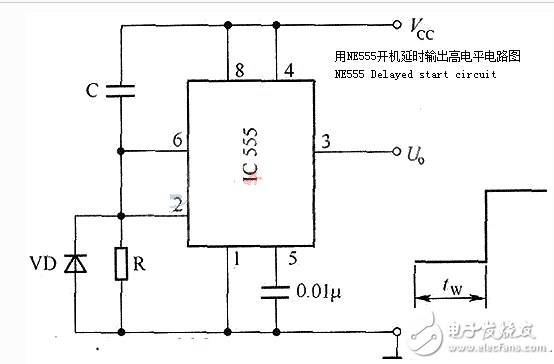

本文主要介绍了ne555延时电路图大全(开机延时输出高电平/自激多谐振荡器)。IC1555时基电路接成占空比可调的自激多谐振荡器。当按下按钮SB后,12V的直流电压加到电路中,由于电容器C6的电压

2018-03-28 16:11

在MSP430单片机的手册中,对于端口复位后的状态,是这样描述的:复位后,所有端口处于输入状态。就这个问题,

2019-08-11 11:28

输入高电平门限Vih:保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为

2018-03-10 09:47

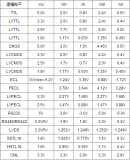

1.CMOS电平: ‘1’逻辑电平电压接近于电源电压,‘0’逻辑电平接近于0V。噪声容限很大 2.TTL电平: 输出高电平

2019-09-14 10:52

当控制信号处于高电平状态时,输入信号的逻辑电平将被反转。例如,若输入信号为高电平,则输出信号为低电平;若输入信号为低电平

2024-02-04 17:35

假设初始状态为输入端和输出端均为高电平,反馈电路没有电流流过。如果输入端的驱动源停止驱动,输入端可凭借反馈电路保持高电平,反馈电路上流过的电流为漏电流(IOZ),一般仅为几毫安。

2018-12-16 11:28

LS、HC 二者高电平低电平定义不同,HC高电平规定为0.7倍电源电压,低电平规定为0.3倍电源电压。

2018-08-02 16:52