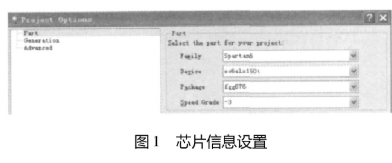

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现

2019-05-24 15:33

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在

2015-02-02 17:32

我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及

2017-02-10 18:40

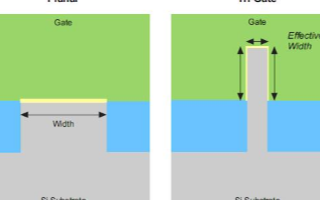

SerDes是一种功能块,用于对高速芯片间通信中使用的数字化数据进行序列化和反序列化。用于高性能计算(HPC)、人工智能(AI)、汽车、移动和物联网(IoT)应用的现代片上系统(SoC)都实现了

2025-03-27 16:18

随着高速数字系统的发展,高速串行数据被广泛使用,内嵌高速串行接口的FPGA也得到大量应用,相应的

2020-07-10 10:11

速度最快的SerDes单一通道的带宽已达112Gbps,支持PAM4编码。如此高的速率,使得在整个系统中实现高速信号布线会面临许多许多设计难题。

2020-03-22 15:37

HTG-703 开发板由 Xilinx Virtex-7 X415T、X485T、X550T 或 X690T 驱动,其非常适合那些要求访问 10G/40G/100G 光学外设、高速扩展连接器、大密度内存以及高带宽 PC 接口的

2017-02-08 17:41

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO到

2023-10-16 14:50

2013年2月,Altera公司与Intel公司共同宣布了Altera下一代最高性能FPGA产品的生产将独家采用Intel的14nm 3D Tri-Gate(三栅极)晶体管技术。这使得Altera

2020-03-12 10:30

。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23