数字频率合成器(Digital Frequency Synthesizer)是一种电子设备,用于生成精确的、可编程的高稳定度的频率信号。它的主要作用是在各种应用中提供精确的频率

2023-06-30 09:15

MAX2902 ISM发送器设计用于与外部频率合成器IC组合,形成完整的TX路径方案。根据系统要求,可以使用小数N分频或整数N分频频率合成器IC。了解两种

2023-03-03 15:22

本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率

2023-10-26 15:30

频率合成器在锁相环 (PLL) 中工作,其中相位/频率检测器 (PFD) 将反馈频率与参考频率的分频版本进行比较(图 1

2023-02-03 10:50

Σ-Δ小数分频频率合成器相位噪声源到输出端的传递函数除VCO相位噪声传递函数为高通滤波传递函数外,其余噪声源到输出端的传递函数均为低通滤波传递函数。本文着重分析Σ-Δ量化噪声对输出相位噪声的影响。

2018-03-21 08:58

本应用笔记介绍了超低抖动时钟频率合成器的设计思路。目标性能在2GHz时<100fs的边沿到边缘抖动。讨论和仿真测试结果表明,目标抖动比最初预期的更难实现。讨论组件变量和权衡,以用于未来的开发工作。

2023-01-16 11:09

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类杂散是实际DDS设计中的 有限

2019-11-14 17:10

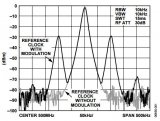

下图所示的是用 Q2230 激励锁相倍频系统实现的一个实际的 频率合成器 。系统时钟采用40 MHz,这样能输出DC~15 MHz、分辨率为0.01 Hz、电压峰一峰值为10 V的正弦波。谱纯度优于

2018-03-17 11:13

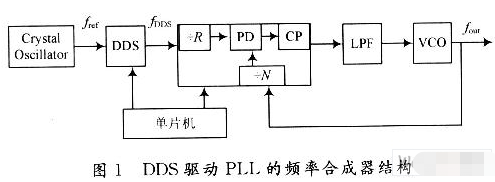

结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频率合成器

2021-06-08 14:07

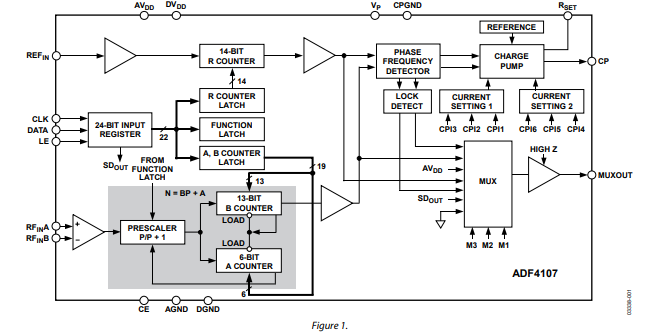

ADF4107频率合成器在无线接收机和发射机的上变频和下变频部分中,可用来实现本振。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器、可编程A和B计数器以及双模预分频器(P/P+1

2025-04-27 15:30