本文主要介绍了静态时序分析 STA。

2023-07-04 14:40

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关

2020-11-25 11:03

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的

2023-03-14 19:10

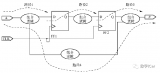

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径

2019-09-01 10:45

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径

2022-09-27 14:45

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序

2023-06-28 09:38

静态时序分析(Static Timing Analysis, 以下统一简称 **STA** )是验证数字集成电路时序是否合格的一种方法,其中需要进行大量的数字计算,需要

2023-06-27 11:43

另一种是手动的方式,在大型设计中,设计人员一般会采用手动方式进行静态时序分析。手动分析方式既可以通过菜单操作(个人理解:通过鼠标点击和键盘输入)进行

2022-08-19 17:10

传统的电路设计分析方法是仅仅采用动态仿真的方法来验证设计的正确性。随着集成电路的发展,这一验证方法就成为了大规模复杂的设计验证时的瓶颈。

2023-07-20 09:46

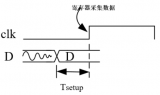

建立时间;保持时间;建立时间裕量;保持时间裕量

2018-12-01 08:20