很明显。对于消费级芯片(如手机CPU,IoT芯片等),由于往往应用在小型移动设备中,低功耗设计就显得尤为重要。

2022-08-17 11:04

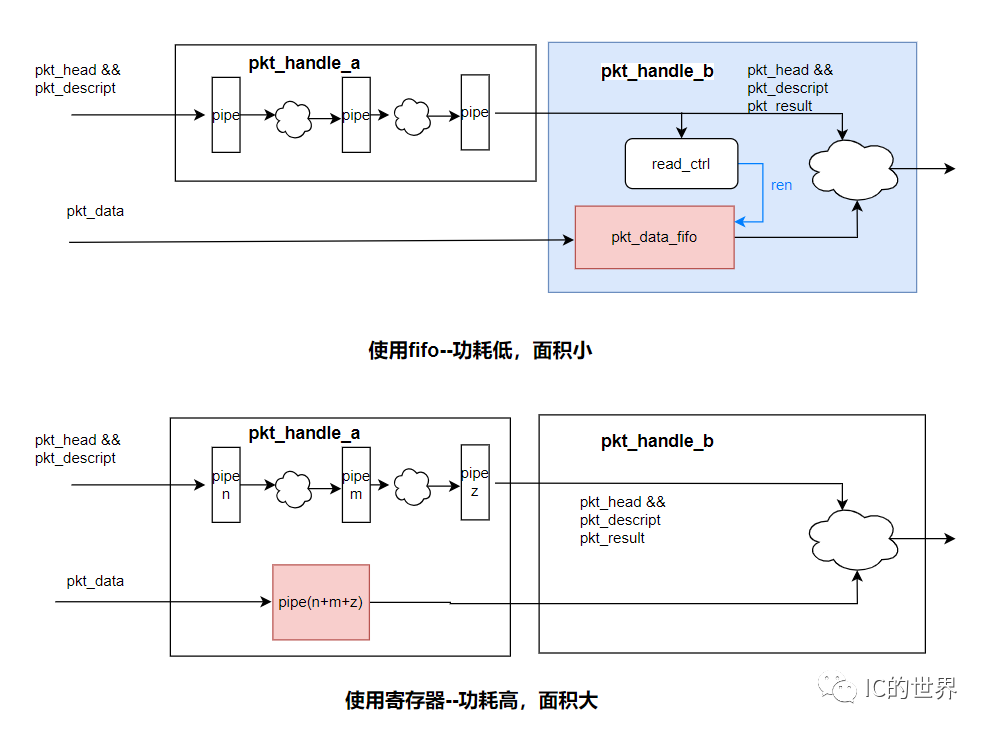

本案例中,我们讲解一种使用fifo节约资源,降低功耗的设计。

2023-12-15 16:34

降低功耗不光能够大大的节约电能还能简化电源部分的设计,甚至可以用于手持设备上面使用,这些都已经越来越成为未来产品的设计方向。

2014-12-23 11:30

人体存在检测(HPD)是视觉传感的一种应用,是了解一个人何时在场,确定其状态和环境的艺术。如果有效实施,与传统方法相比,它有可能获得许多好处,特别是在安全性和降低功耗方面。

2023-04-24 11:01

对大多数应用来说,人机界面、低功耗和无线连接集成是单片机(MCU)的三大前沿技术。而新型技术的推出都是以一定的应用为背景的。

2018-05-22 07:13

在90nm工艺时,电流泄漏问题对ASIC和FPGA都变得相当严重。在65nm工艺下,这一问题更具挑战性。为获得更高的晶体管性能,必须降低阈值电压,但同时也加大了电流泄漏。Xilinx公司在降低电流

2020-07-21 17:56

静态功耗是指一个电路维持在一个或另一个逻辑状态时所需的功率。可以通过观察电路中每个电阻元件的电流I和压降V来计算每个元件的功率VI,并求和得到总功率,这就是没有负载的情况下的静态功耗,也就是我们通常在数据手册上看到的标称值。

2019-07-16 14:41

在绝大部分使用电池供电和插座供电的系统中,功耗成为需要考虑的第一设计要素。Xilinx决定使用20nm工艺的UltraScale器件来直面功耗设计的挑战,本文描述了在未来的系统设计中,使用Xilinx 20nm工艺的UltraScale FPGA来

2018-07-14 07:21

我们之所以选择 A53,是因为处理器供应商提供了广泛的片上系统 (SoC),并且 FPGA 供应商已将其整合到他们的新一代 MPSoC FPGA 中。所有三个模型都在大约两周的时间内构建和评估。

2022-08-09 11:14

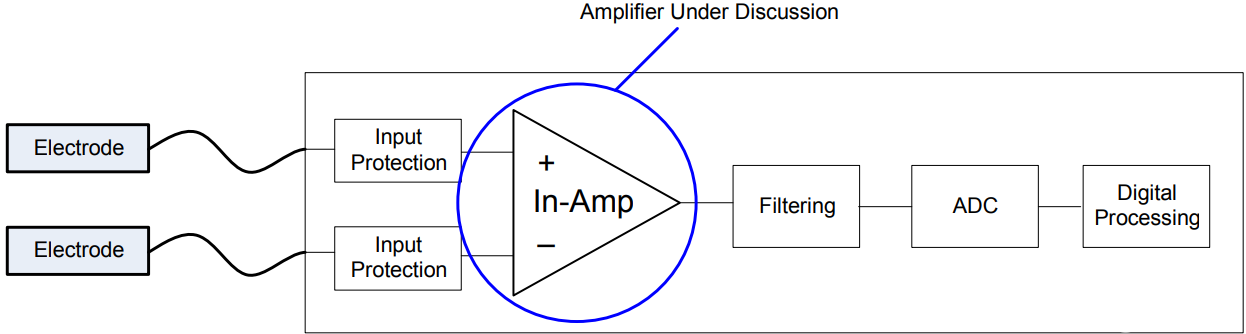

二十多年来,CareFusion Nicolet一直是脑电图诊断系统领域的先驱发展。EEG(脑电图)监测用于睡眠研究、脑图谱和 ICU 患者大脑活动的神经学分析。随着脑研究和脑电图诊断的不断突破,脑电监测设备有望在传统临床环境之外的新环境中运行。这些新环境带来了新的设计挑战 — 本文解决了其中的一些挑战。

2023-01-31 09:16