CP是wafer level的chip probing,是整个wafer工艺,包括backgrinding和backmetal(if need),对一些基本器件参数的测试,如vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,一般测试机台的电压和功率不会很高;

2023-11-23 17:38

蓝牙技术联盟(Bluetooth SIG)对蓝牙标准进行了更新,正式发布了最新的4.1版本。##支持“多连一”##简化设备连接##附录

2014-06-11 11:02

关于Verilog语言的官方标准全称是《IEEE Std 1364-2001:IEEE Standard Verilog® Hardware Description Language》。其中包括27章以及8个附录,真正对于电路设计有用的内容大约1/3的样子。

2018-07-06 09:59

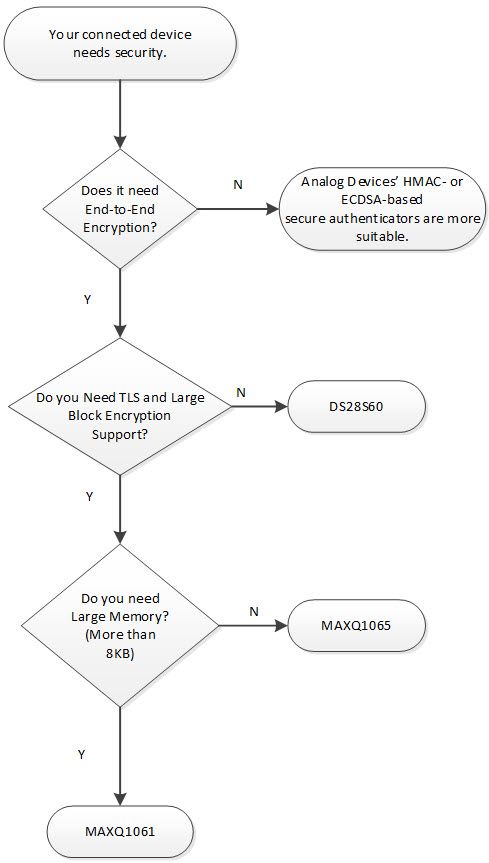

本应用笔记讨论了DS28S60、MAXQ1061和MAXQ1065的主要特性。它比较设备之间的功能,然后为用户提供有关如何以及何时部署每个设备的一些相关建议。附录提供了一些特定的设备功能和性能比较。

2023-02-17 11:28

帕塞瓦定理的两种常见形式, 在我的《随机信号分析》里面作为附录4, 即帕塞瓦定理的两种常见形式, 第三种形式即不常用的形式, 明天再给读者介绍. 我自己也要去翻资料, 找到帕塞瓦定理第三种形式的最标准的表述.

2018-04-02 11:13

本应用笔记介绍如何使用DS31256的接收BERT功能执行分数T1(FT1)环路或环路下降检测(V.54),如分数T1.403附录B规范中所述。工作算法和编码示例说明了DS31256易于适应终端用户应用。

2023-02-22 10:08

我们没有测量硬件的峰值理论FLOPS,而是尝试估计执行的实际操作的数量。我们将加法和乘法作为单独的操作,将任何相加或相乘计算为一个操作,而不考虑数值的精度(因此“FLOP”不太适当),并且我们忽略了集成模型。在本文附录中提供了该图表的示例计算。

2018-05-19 07:46

这篇应用笔记介绍了利用DS31256的接收BERT功能实现分数级T1 (FT1)上环回或下环回检测(V.54)的方法,详细说明请参考分数级T1.403附录B规范。所提供的算法和示例代码简化了DS31256最终用户的设计。

2023-06-16 15:35

熟习一门硬件设想言语(VHDL或Verilog HDL),由于不论在哪种运用范围,HDL言语都是FPGA开拓的根底。目前国际运用Verilog HDL言语的开拓职员较多一些,因而引荐读者进修Verilog HDL。正因如此,本书的实例都经过Verilog HDL完成,并在附录中给出其扼要的语法阐明。

2019-01-17 11:44

集成电路的设计在很大程度上依赖于软件工具。以前,用于生产集成电路的工具规则来自IEC 61508-2:2010附录F,并且首选经过验证的正在使用的工具。经过验证的使用现已弃用,对用于生产集成电路的工具的要求将与用于生产安全系统的任何其他硬件或软件元件的要求相似。

2023-06-28 14:43