Altera的Cyclone V FPGA目前是业界系统总成本和功耗最低的FPGA,那我们该怎样为自己的设计选择Altera

2013-02-26 10:34

解读的内容仅限 Faster Transformer v1.0 版本,更高版本的源码将在后续文章中继续解读。

2023-09-08 10:20

时序逻辑电路对于组合逻辑的毛刺具有容忍度,从而改善电路的时序特性。同时电路的更新由时钟控制。

2018-11-24 11:17

TDK公司 扩展了编程工具链,磁传感器编程器(MSP)V1.0可以方便地对Micronas多种产品编程。MSP V1.0替代APB 1.5 及其他现有的编程工具,其集合了

2018-09-29 09:25

模块的模板包括了输入输出信号列表、信号定义,组合逻辑和时序逻辑等,这是一个模块常用的组件。学员只需要理解各个部分的意义,按要求来填空就可以,完全没有必要去记住。我看很多学员刚开始学习时,花费大量的时间去记住、背熟模块,这是没有意义的。

2018-04-20 15:40

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足

2017-11-18 04:32

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43

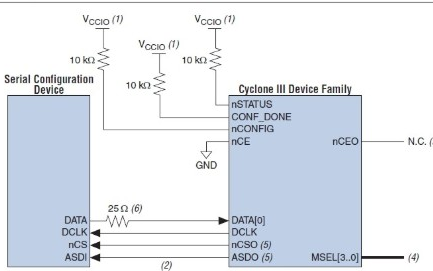

很多人第一次接触Altera Cyclone系列FPGA的时候,可能会被其复杂的专用管脚给搞混淆,在这里我们Altera Cyclone系列FPGA的专用管脚一一列出供

2020-01-26 17:50