锁相环(PLL)和压控振荡器(VCO)以特定频率输出RF信号,理想情况下,该信号将是输出端存在的唯一信号。实际上,输出端存在不需要的杂散信号和相位噪声。本文讨论如何仿真和消除一种更麻烦的

2023-01-08 15:40

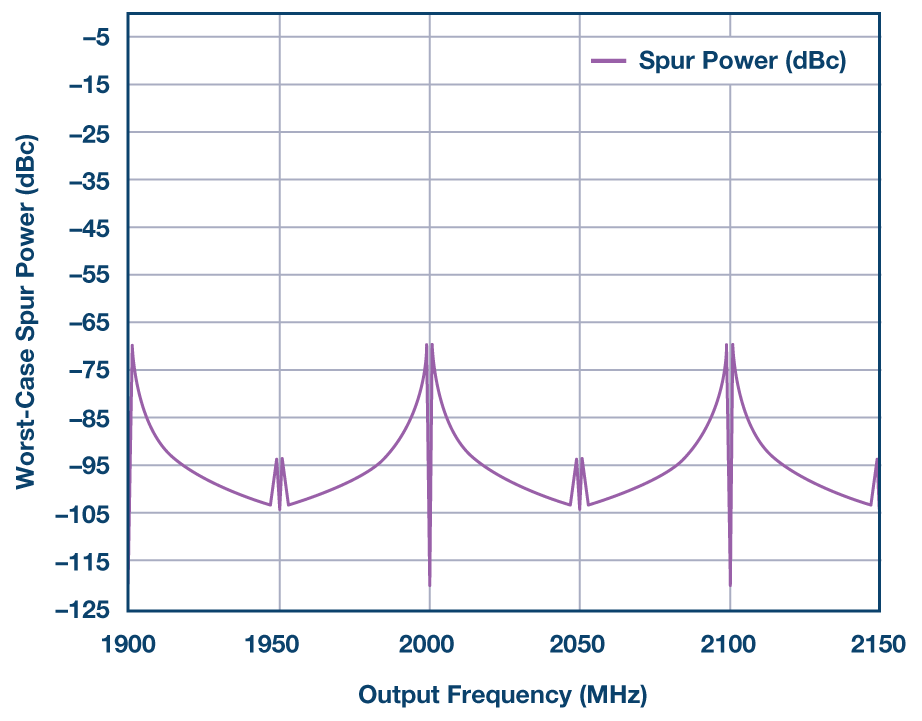

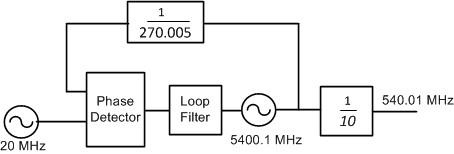

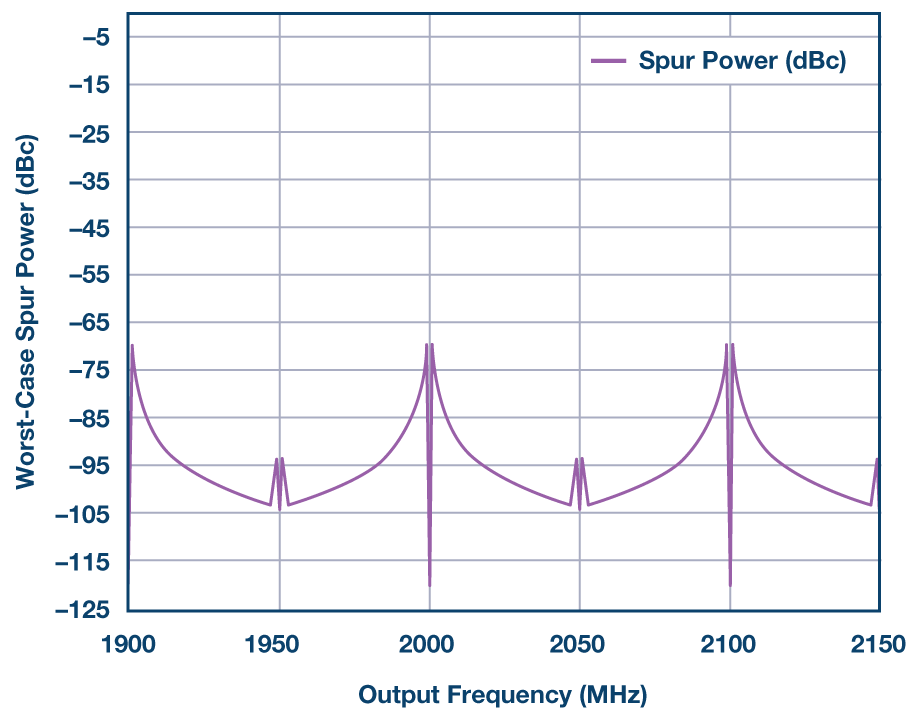

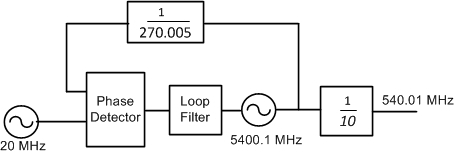

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数

2023-04-18 09:29

假设某个调制方案指出整数边界杂散功率高于–80 dBc的通道不可用;那么图10中大约1%的通道不再可用。为了克服这个问题,ADIsimFrequencyPlanner可以优化PLL/VCO配置,以减少并在大多数情况下

2023-02-01 11:54

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数

2022-02-06 09:29

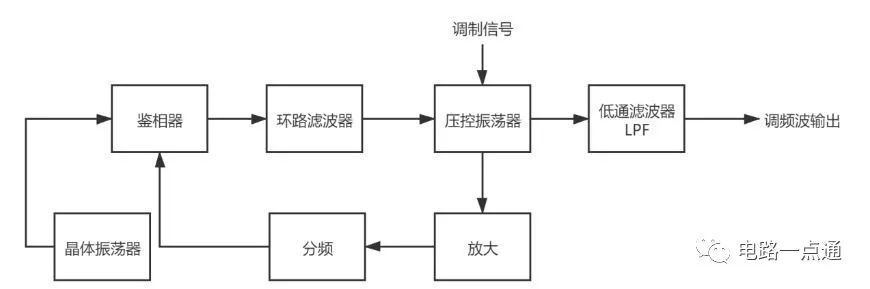

锁相环电路,是调频电路的重要组成之一,锁相环电路的原理的认识是DDS学习的一个重点之一。

2023-07-24 15:37

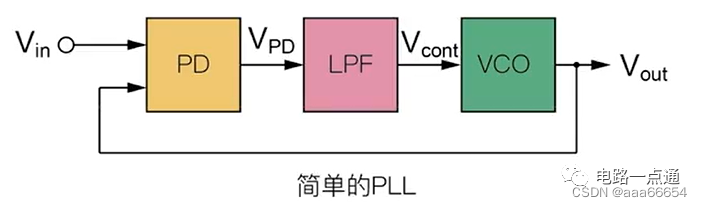

锁相环接收一个它所锁定的信号,然后可以从其内部的VCO输出这个信号。乍一看,这可能不是特别有用,但是在你完全明白它,就有可能开发出大量的锁相环应用。

2023-07-17 09:09

锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和

2022-12-23 14:03

锁相环是一种利用相位同步产生电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。

2023-06-25 09:22

锁相环(Phase-LockedLoop, PLL),是一种反馈控制电路,电子设备正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的,它可用来从固定的低频信号生成稳定的输出高频信号。

2024-08-06 15:07

锁相环(Phase Locked Loop,简称PLL)是一种在电子系统中广泛应用的负反馈控制系统,其主要作用是实现输入信号与输出信号之间的相位同步。在现代通信、雷达、导航、测量等领域,锁相环都发

2024-05-24 16:28