DDR SDRAM的接口特性:其输入输出引脚与SSTL-Ⅱ电气特性兼容,内部提供了DDR触发器、锁相环等硬件资源。使用这些特性,可以比较容易地设计性能可靠的高速DDR RAM控制器。本文介绍一种采用FPGA与IP来实现DDR RAM控制和验证的

2017-11-24 16:00

FPGA是现场可编程门阵列的简称,是新一代的自动调谐控制单元,它采用VHDL语言进行现场编程,其特点是:I/O资源丰富,运算速度快(ns级),集成度高,稳定性好,包含的LUT和触发器数量丰富等等

2017-11-23 14:21

新唐的ISD18C00 ChipCorder®能提供高品質、單晶片、單訊息,以及可由使用者選擇6至16秒持續時間的錄音/回播解決方案。CMOS裝置包括一個晶片內建振盪器

2019-11-22 16:43

VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。依据VGA显示原理,介绍了利用FPGA实现对VGA图形控制器的Verilog设计方法。详细描述了各硬件模块的工作原理及实现途径,并给出了软件设计思路。

2019-06-29 10:05

毛刺现象在FPGA设计中非常普遍, 而毛刺的出现往往导致系统结果的错误。本文从FPGA的原理结构的角度深入探讨了毛刺产生的原因及产生的条件,总结了多种不同的解决方法,并结合具体的应用对解决方案进行

2017-11-22 14:24

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种

2018-07-17 08:33

的思想用于弹速补偿,提高了相参积累后的信噪比,并在FPGA中完成硬件实现,仿真实验表明使用FPGA实现弹速补偿方法具有实时性高、处理速度快、精度高等有优点。

2019-03-30 09:56

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、

2014-08-28 17:10

高诱电系的积层陶瓷电容器的静电容量,以经过125℃以上的热处理24小时后的值作为基准,与时间成对数关系直线性下降。请参考如下村田制品静电容量老化特性的代表例子。

2018-04-02 15:32

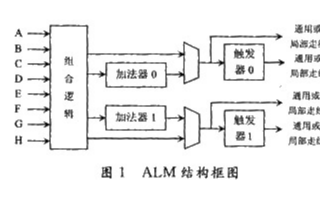

图2列出了和传统的4输入LUT结构的FPGA相比较,采用ALM的StratixⅡFPGA器件例化3输入加法器的优势。从图2中可以清楚地看出,对于同样3个2 b数据相加的逻辑结构,传统4输入LUT结构

2020-03-03 10:45