下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

348例实用电路图分享

2022-11-21 09:49

导语:均匀性在芯片制程的每一个工序中都需要考虑到,包括薄膜沉积,刻蚀,光刻,cmp,离子注入等。较高的均匀性才能保证芯片的产品与性能。那么片内和片间非均匀性是什么?如何计算?有什么作用呢?

2023-11-01 18:21

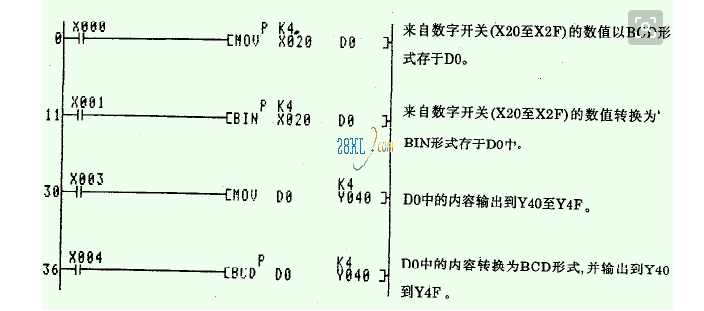

把二进制数转换成 BCD 码,是很常见的,做而论道以前也发表过这样的程序。 但是,过去都是用寄存器,如果要求用片内RAM单元,就少见了。 当然,也可以把片内RAM单元

2018-05-19 01:18

MAX5134–MAX5137是具有引脚兼容和软件兼容的16位DAC和12位DAC系列产品。MAX5134/MAX5135为低功耗、4路16/12位、带缓冲的电压输出、高线性度DAC。

2013-03-25 16:42

LMX2820 是一款高性能宽带合成器,可生成 45 MHz 至 22.6 GHz 范围内的任何频率。具有–236 dBcHz 品质因数和高相位检测器频率的高性能PLL 可以实现极低的带内噪声和集成

2021-06-12 09:05

OAD( ), 即Over the Air Download,是通过无线的方式远程更新固件的一种方法。On chip,就是片上, 升级的对象不需要外挂Flash, 通过芯片片内Flash完成新固件

2018-06-17 04:56

本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过程和步骤。从规格选择、电路配置

2023-10-26 15:30

SLM片内监控IP数据分析为高价值应用提供了更为自动化的数据分析手法。

2024-07-16 15:05