静态时序分析是一种重要的逻辑验证方法,设计者根据静态时序分 析的结果来修改和优化逻辑,直到设计满足要求。

2022-11-11 09:42

虚拟FPGA逻辑验证分析仪的设计 随着FPGA技术的广泛使用,越来越需要一台能够测试验证FPGA芯片中所下载电路逻辑时序是否正确的仪器。目前,虽然Agilent、Te

2008-10-15 08:56

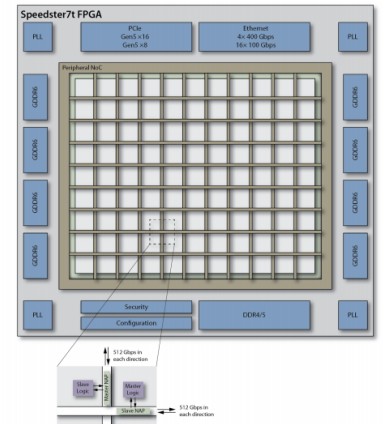

基于团队的协同化 FPGA 设计并不是一个新的概念,但是底层架构和布线依赖于 FPGA 的其他部分,从而使得实现这个简单概念非常具有挑战性。一旦一个团队完成了设计的一部分,另一个设计其他部分的团队在尝试访问设备另一端的资源时,通常会遇到挑战,因为需要在已经完成的设计部分进行布线。同样,对一部分已进行设计布线的 FPGA 的区域或大小进行更改,可能会对所有其他 FPGA 设计模块产生连锁影响。

2020-08-10 16:25

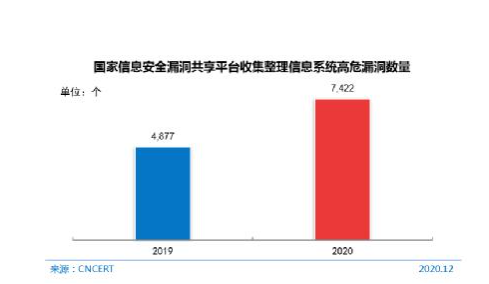

大量简单的业务逻辑被用于构建复杂而又丰富的业务逻辑,设计或实现上的偏差或缺陷都会导致漏洞的产生。

2021-04-09 09:23

芯片设计的逻辑仿真和数字验证是芯片设计流程中非常重要的一环,它主要用于验证芯片的功能和时序等方面的正确性。下面是逻辑仿真和数字验

2023-09-14 17:11

要说ASIC设计者的经验有所提示的话,那么将来的百万门级可编程逻辑设计中验证会耗费大半的设计周期。随着设计复杂度的增加,传统的设计验证方

2009-06-20 11:46

Cadence Low-Power Solution是用于低功耗芯片的逻辑设计、验证和实现的完全集成的、标准化的流程,将领先的设计、验证和实现技术与Si2Common Power Format

2018-11-13 11:30

寄存器传输级(RTL)验证在数字硬件设计中仍是瓶颈。行业调研显示,功能验证占整个设计工作的70%.但即使把重点放在验证上面,仍有超过60%的设计出带需要返工。其主要原因是在功能

2018-11-23 09:30

领袖、专家及产业上下游分享前沿技术。 分论坛一:数字逻辑设计与验证领域 时间:9月18日 地点:武汉· 中国光谷科技会展中心 三层多功能厅1 演讲主题 全流程数字验证平台,让验

2023-08-29 09:10