静态时序分析是一种重要的逻辑验证方法,设计者根据静态时序分 析的结果来修改和优化逻辑,直到设计满足要求。

2022-11-11 09:42

虚拟FPGA逻辑验证分析仪的设计 随着FPGA技术的广泛使用,越来越需要一台能够测试验证FPGA芯片中所下载电路逻辑时序是否正确的仪器。目前,虽然Agilent、Te

2008-10-15 08:56

基于虚拟仪器技术的逻辑验证分析仪该怎样去设计?

2021-05-12 06:22

虚拟FPGA逻辑验证分析仪的工作原理是什么?虚拟FPGA逻辑验证分析仪有哪几个主要工作环节?

2021-04-29 07:07

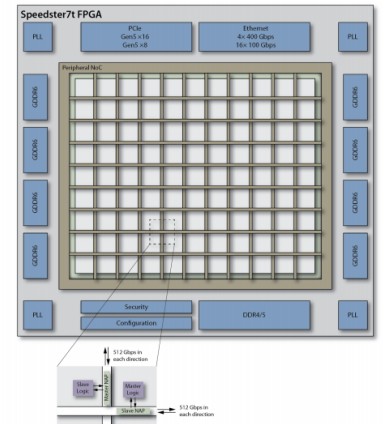

基于团队的协同化 FPGA 设计并不是一个新的概念,但是底层架构和布线依赖于 FPGA 的其他部分,从而使得实现这个简单概念非常具有挑战性。一旦一个团队完成了设计的一部分,另一个设计其他部分的团队在尝试访问设备另一端的资源时,通常会遇到挑战,因为需要在已经完成的设计部分进行布线。同样,对一部分已进行设计布线的 FPGA 的区域或大小进行更改,可能会对所有其他 FPGA 设计模块产生连锁影响。

2020-08-10 16:25

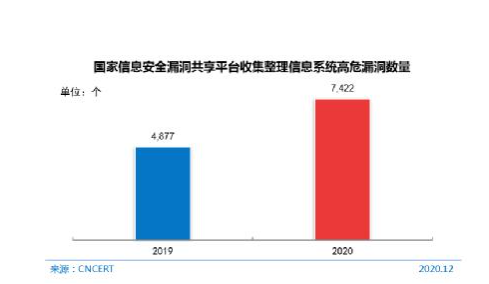

大量简单的业务逻辑被用于构建复杂而又丰富的业务逻辑,设计或实现上的偏差或缺陷都会导致漏洞的产生。

2021-04-09 09:23

2014-09-23 10:25