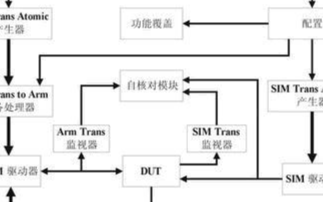

本文设计了一款支持多接口、多协议的无线局域网802.11n(1T1R)的SoC芯片。该SoC芯片集成了SDIO,SPI,UART等接口。为了验证各个接口是否能够达到设计

2018-06-29 15:35

IP核验证平台采用6层板PCB设计,使用独立的外部时钟同步芯片,可以为PCI及其它接口提供稳定的零延迟时钟系统电路,满足PCI总线的时钟要求,使验证平台高速,稳定,可靠的工作。

2012-01-17 14:02

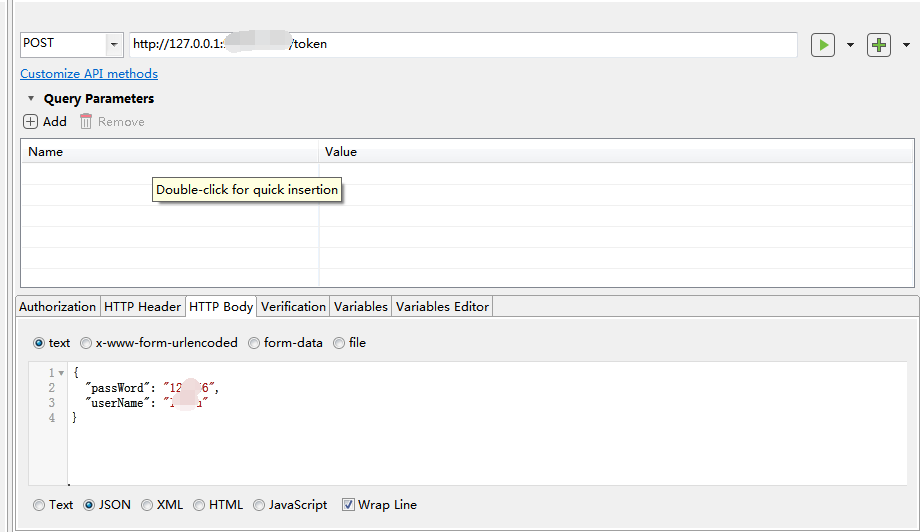

最近抽时间接触了一下Katalon Studio(后面简称KS),并且利用KS做了一些接口测试的试验,感觉还不错,不过其中接口授权中缺少通过token动态验证的方案,虽

2019-04-06 17:34

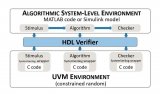

在本文中,我们将以西门子EDA处理器验证应用程序为例,结合Codasip L31这款广受欢迎的RISC-V处理器IP提供的特性,来介绍一种利用先进的EDA工具,在实际设计工作中对

2023-07-10 10:28

基带射频接口模块包含射频接口的接收通路模块和发送通路模块。基带射频接口模块架构图如图2所示。此射频接口模块采用AXI标准总线协议,

2018-03-22 09:06

为降低成本,提高设计灵活性,提出一种基于FPGA的1553B总线接口方案;采用自顶向下的设计方法,在分析1553B总线接口工作原理和响应流程的基础上,完成了接口方案各FPGA功能模块设计;对关键模块

2017-11-17 13:47

测试层用于对DUT的逻辑功能进行验证。这一层主要是用户为了验证DUT的逻辑功能而编写的不同测试例,在测试例中可以对各个模块的限制条件进行修改。通过对不同测试例运行结果的统计,可以查看DUT的功能覆盖率,只有功能覆盖率

2021-03-22 15:27

RISC-V的开放性允许定制和扩展基于 RISC-V 内核的架构和微架构,以满足特定需求。这种对设计自由的渴望也正在将验证部分的职责转移到不断壮大的开发人员社群。然而,随着越来越多的企业和开发人员转型RISC-V,大家才发现处理器

2023-07-10 09:42

信号处理集成电路(IC)设计的验证带来了一些独特的挑战,这些挑战可能会给传统的测试方法带来压力。滤波器、混频器和其他高级信号处理功能的算法复杂性需要严格的验证,以确保实

2025-09-23 17:32

本文实现的基于FPGA的PCIe总线接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基础上实现的,利用Synopsys VIP验证环境进行了功能仿真验证,并

2018-01-11 10:57