跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34

方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时

2021-05-19 11:25

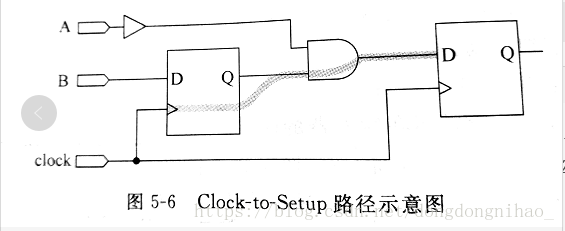

该条路径包括了触发器内部clock-to-Q的延迟,触发器之间的由组合逻辑造成的路径延迟以及目标触发器的建立时间,其延时是数据从源触发器开始,在下一个时钟沿来到之前通过组合逻辑和布线的最大时间

2024-01-18 16:31

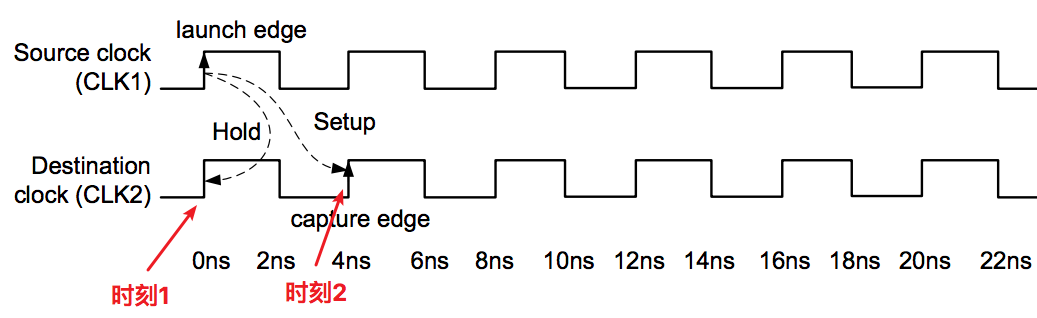

在单时钟域下,发送端和接收端时钟是同频同相的,如果两个时钟同频不同相怎么处理?

2020-11-18 13:56

OFFSET语句:OFFSET说明了外部时钟和与其相关的输入,输出数据引脚之间的时序关系。

2020-11-25 14:23

电磁干扰(EMI)是指电子设备之间或电子设备与其周围环境之间的电磁相互作用,导致其中一个或多个设备的性能受到干扰或损坏的现象。

2023-06-28 16:21

当 RPQF 值越趋近于 1,则表示信号布线与与回流路径是越贴近的,越高则代表回流路径越曲折绕越远的路径。

2023-04-17 10:28

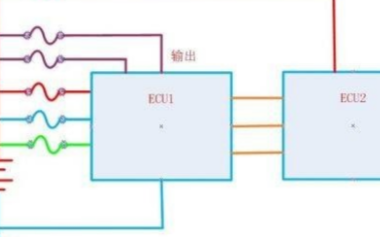

在汽车电子中有个非常重要的事情,就是潜在路径分析这个内容,如果搜索这个词,你在网上很少会发现它,事实上在国内一般只有航天航空军工去关注它。

2020-01-19 10:01