在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25

该条路径包括了触发器内部clock-to-Q的延迟,触发器之间的由组合逻辑造成的路径延迟以及目标触发器的建立时间,其延时是数据从源触发器开始,在下一个时钟沿来到之前通过组合逻辑和布线的最大时间

2024-01-18 16:31

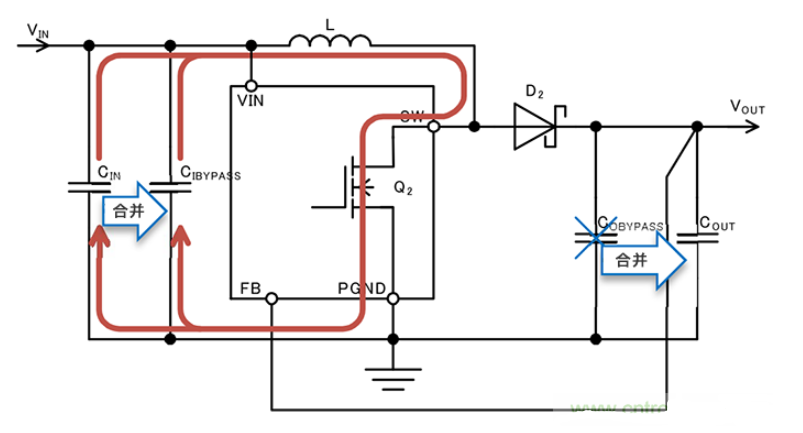

请看开关晶体管Q2关断时的电流状态(图中红线)。电感L的作用是即使开关晶体管Q2 OFF时也可保持在此之前的电流值。

2021-03-12 10:47

随着低空经济的蓬勃发展与无人机(UAV)产业向长航时、高可靠、多场景应用的深度进军,作为飞行器“心脏”能量库的燃油存储系统,其性能已成为决定飞行器能力上限的核心关键之一。

2025-12-19 10:01 湖南泰德航空技术有限公司 企业号

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建

2022-08-02 09:54

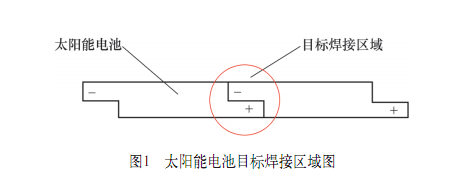

根据太阳能电池装配特点,选择出符合柔性装配系统的焊接方式。针对抓取机械手和焊接机械手的运动特点,分别设计两者运动路径方案;通过合理简化运动模型,对抓取机械手和焊接机械手分别进行运动路径分析计算,优化机械手的运动路径,

2018-01-13 11:01

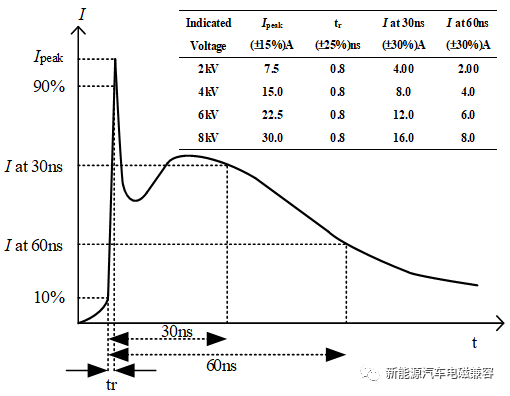

好像任何一个行业的EMC都离不开ESD测试, ESD问题排查中,最重要最难的无疑是静电路径问题了。 本次就和大伙稍微探讨下ESD电流路径的分析,哪怕在为大家排查静电问题的时候提供一丝丝有益的思路,我就觉得没有白写。

2023-10-17 15:55

我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC

2017-11-18 04:04

电流离开门电路A,经由信号返回路径X流回源端。由于电流路径X、Y和Z相互重叠,路径X的磁场将在信号路径Y和Z上感应出噪声电压。 因为

2018-04-16 12:32

Dijkstra(迪杰斯特拉)算法是最短路算法的经典算法之一,由E.W.Dijkstra在1959年提出的。该算法适于计算道路权值均为非负的最短路径问题,可以给出图中某一节点到其他所有节点的最短路径,以思路清晰,搜索准确见长。相对的,由于输入为大型稀疏矩阵,又具有

2018-05-24 10:27