求解路径分析表示根据要求解的阻抗查找最快、最短甚至是最优的路径。如果阻抗是时间,则最佳路线即为最快路线。如果阻抗是具有实时或历史流量的时间属性,则最佳路径是对指定日期和时间来说最快的

2019-06-03 08:04

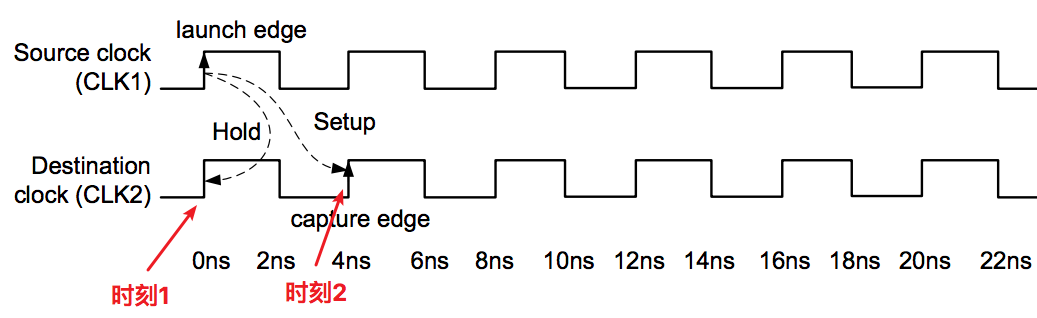

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11

(In-DesignAnalysis,设计同步分析)的 ReturnPath 分析功能,在 PCB 设计过程中进行回流路径分析,帮助工程师快速找出那些高速信号的回流路径

2021-02-05 07:00

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25

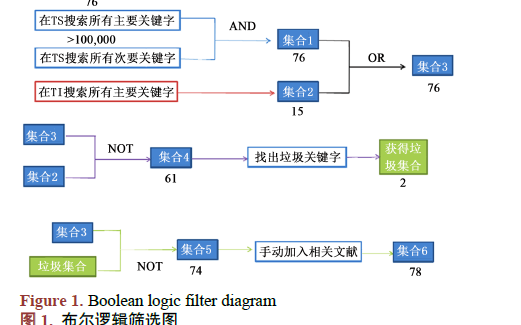

通过引文分析和主路径分析的方法,将Web of Science (WOS)数据库中以负面口碑为主题的文献作为研究对象,研究负面口碑的重要文献与逻辑演化路径。研究发现:Richins (1983

2018-12-20 11:20

电子发烧友网为你提供散热障碍与散热路径分析资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-12 08:45

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34

方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时

2021-05-19 11:25

该条路径包括了触发器内部clock-to-Q的延迟,触发器之间的由组合逻辑造成的路径延迟以及目标触发器的建立时间,其延时是数据从源触发器开始,在下一个时钟沿来到之前通过组合逻辑和布线的最大时间

2024-01-18 16:31

在单时钟域下,发送端和接收端时钟是同频同相的,如果两个时钟同频不同相怎么处理?

2020-11-18 13:56