本应用笔记介绍了超低抖动时钟频率合成器的设计思路。目标性能在2GHz时<100fs的边沿到边缘抖动。讨论和仿真测试结果表明,目标抖动比最初预期的更难实现。讨论组件

2023-01-16 11:09

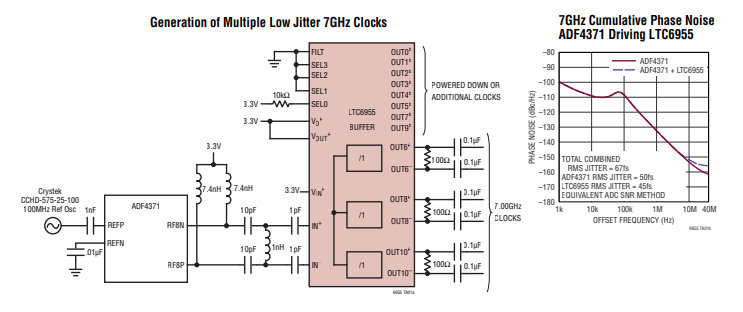

LTC6955 是一款具有十一个输出的高性能超低抖动扇出时钟缓冲器。它的 4 引脚并行控制端口允许多种输出设置(3 个和 11 个之间的任意个输出)以及完全关断。利用该并行端口还能够反转交流输出的输出极性,从而简化采用顶部和底部板布线的设计。

2025-04-09 15:19

随着数据速率的增加,链路抖动允许量变得越来越严格。硬件工程师将主要精力放在如何使他们的整个线路卡能够支持最大吞吐量,而为基准时钟产生的随机抖动分配尽可能小的允许量。针对基准时钟,对于一条25GbE

2023-04-17 10:37

本文介绍了Si54x系列主要特性,功能框图,通用振荡器评估板Si5xxUC-EVB主要特性,框图和电路图。

2018-06-17 16:42

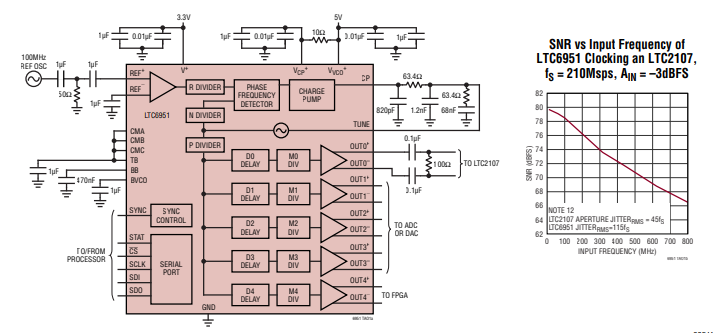

LTC6951 是一款具一个全集成型 VCO 的高性能、低噪声锁相环 (PLL)。低噪声 VCO 未使用外部组件,并且在没有外部系统支持的情况下在内部校准至正确的输出频率。

2025-04-10 09:30

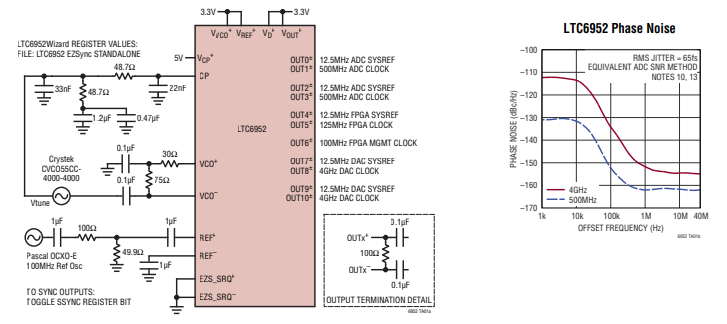

LTC6952 是一款高性能、超低抖动 JESD204B/C 时钟生成和分配 IC。该器件包括一个锁相环 (PLL) 内核,由基准分频器、具有锁相指示器的相位频率检波器 (PFD)、超低噪声充电

2025-04-09 17:26

LTC6953 是一款高性能、超低抖动的 JESD204B/JESD204C 时钟分配 IC。LTC6953 的 11 个输出可配置为最多 5 个 JESD204B/JESD204C

2025-04-16 14:28

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe

2023-06-08 15:29

随着现代电子系统对高精度、高可靠性时钟信号需求的不断提升,时钟抖动成为影响系统性能的关键因素。核芯互联科技有限公司重磅推出CLF04828超低噪声去抖时钟,凭借其领先的双PLL架构、超低相位噪声和灵活的输出配置,为多

2025-03-04 12:38