高速信号走线规则教程 随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的关注。高速PCB设计的成功,对EMI

2009-04-15 08:49

射频(RF)PCB走线规则是确保无线通信设备性能的关键因素之一。在高频信号设计中,PCB走线不仅承载着电流,还对信号的完整性和质量有着显著影响。

2024-05-16 18:18

本文详细阐述了pcb电源线走线规则。芯片的电源引脚和地线引脚之间应进行去耦。去耦电容采用0.01uF的片式电容,应贴近芯片安装,使去耦电容的回路面积尽可能减小。

2020-02-24 16:47

在高速数字电路设计中,信号完整性(SI)是确保系统性能和可靠性的核心要素。高速信号线的走线规则对于维持信号质量、减少噪声干扰以及优化时序性能至关重要。本文将深入探讨高速信号线走线的关键

2025-01-30 16:02

IIC通信是一种双线制串行总线,由SDA(串行数据线)和SCL(串行时钟线)两条线组成。SDA线用于传输数据,而SCL线则用于传输时钟。在IIC通信中,数据的传输是由主设备发出开始信号,然后将数据发送给从设备,最后发出停止信号结束传输。

2023-08-26 12:02

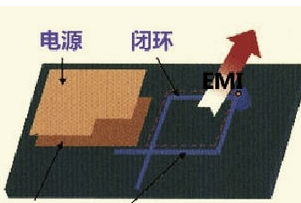

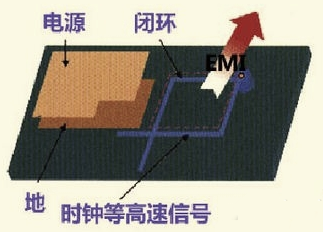

规则一 规则 图1 如图1所示,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或者只屏蔽了部分,都会造成EMI泄漏。建议屏蔽线,每1000mil,打孔接地。 规则

2018-09-12 09:10

差分线上串共模电感,阻抗差不多几十欧姆,共模电感由两根导线同方向绕在铁芯材料上,当共模电流通过时,共模电感会通过磁通量叠加产生高阻抗,当差模电流通过时,共模电感通过磁通量相互抵消产生小阻抗,这样对共模噪声产生很好哦的抑制效果,同时共模电感的差模阻抗比较小,所以对信号的不会有大 的影响;

2020-05-04 18:03

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。##在高速的PCB设计中,时钟等关键

2016-04-26 14:00

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35