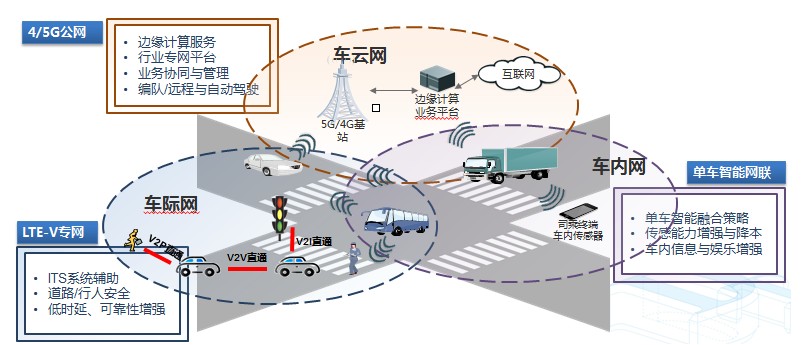

大唐电信集团旗下大唐移动持续致力于超低时延、高可靠性、强安全性等核心关键技术的研究,积极推动V2X在中国乃至全球的产业化进程,促进智慧交通应用的落地开花。

2018-12-29 09:33

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。

2017-02-11 13:28

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。

2017-02-11 13:04

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

2017-02-11 13:11

注意:当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己。 需要说明的是在FPGA/CPLD内部结构是一种标准的宏单元,下图是Xilinx公司的Spartans II系列器件的一个标准宏单元。虽然不同的厂家的芯片宏单元的结构不同,但概括而言都是由一些组合逻辑外加一或二个触发器而构成。在实际应用中,当一个模块内的组合逻辑被使用了那么与其对应的触发器也就不能用了;同样如果触发器单元被用了那么组合逻辑单元

2017-02-11 13:14

当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/CPLD相连接的芯片的工作时钟大多数情形下与FPGA的时钟同源,如果输出的信号经过时钟锁存可以起到如下的作用:

2017-02-11 13:18

电信企业计费(Billing)系统是电信支撑系统BSS/OSS 的核心。

2014-08-20 16:47

广大无线电爱好者都知道无线电通信是利用电磁波在空间的传播来传递信息的。 但是电磁波又是怎样把信息传递出去的呢?对于无线电信号是怎样发送和接收的,估计大部分人就不太清楚了,来聊聊无线电信号是怎样发送和接收的,我们以话音为例说明无线

2019-03-09 10:17

肌电信号作为生物电信号的一种,是产生肌肉动力的电信号根源,它是肌肉中很多运动单元的动作电位在时间和空间上的叠加,很大程度上上反应了神经、肌肉的运动状态。从获取肌电信号

2018-06-07 11:27

电信宽带是中国电信运营商向电信用户提供接入互联网服务的总称,以“天翼宽带”统一的业务品牌向用户呈现,通过统一的天翼宽带客户端,向用户提供无缝覆盖宽带接入服务,并集成统一通讯录、短信、天翼Live、网盘、安全专家、天翼

2017-12-26 14:12