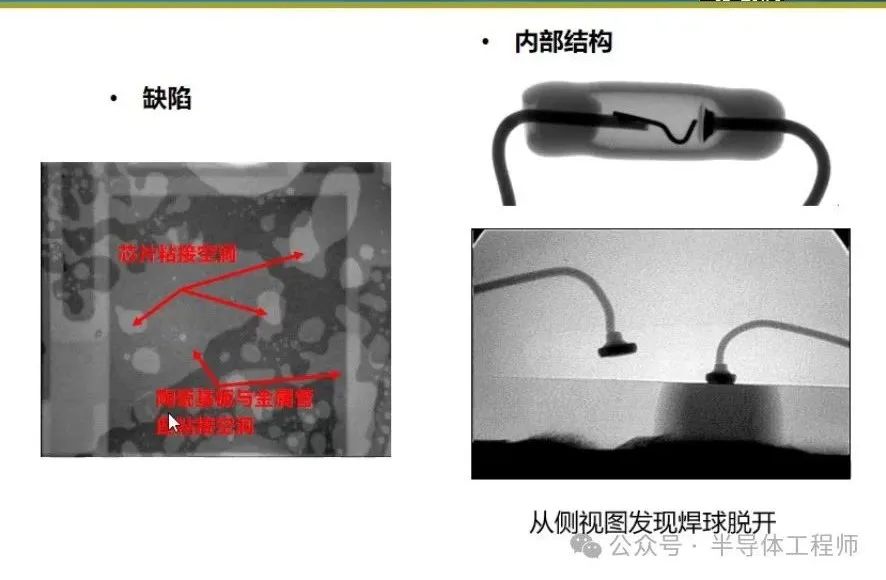

在芯片失效分析中,常用的测试设备种类繁多,每种设备都有其特定的功能和用途,本文列举了一些常见的测试

2024-08-07 17:33

视频时钟合成芯片(Video Clock Synthesizer,VCS)是一种用于生成和调整视频信号时钟的电子设备,广泛应用于视频处理、显示、传输等领域。它能够将输入的时钟信号转换成所需的视频格式

2024-10-10 11:17

探针卡是半导体晶圆测试过程中需要使用的重要零部件,被认为是测试设备的“指尖”。由于每一种芯片的引脚排列、尺寸、间距变化、频率变化、

2023-05-08 10:38

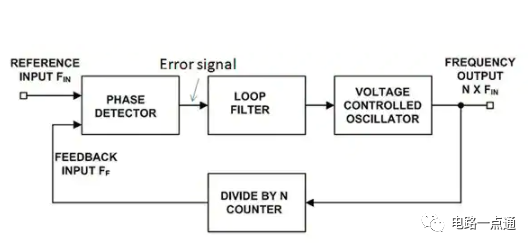

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。因此,在包括无线电接收器和测试

2023-07-10 09:57

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

IC测试原理和设备教程在内容、目的和关注点上存在显著的区别。 IC测试原理 内容 : IC测试原理主要探讨的是对集成电路(Integrated Circuit,简称IC

2024-09-24 09:51

信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出

2017-12-13 16:26

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的

2017-05-22 09:16

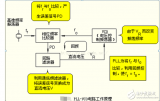

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22