在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用

2018-12-22 15:14

如何在开发IP的同时去巩固集成和复用覆盖率?IP的某些功能和性能是可以配置的,需要考虑的是IP被各种合理配置后的工作是否都能够正常,将功能覆盖率先整理为层次化的抽象功能

2018-02-18 12:08

引言 在芯片设计中,IP设计(Intellectual Property design)和SOC设计(System on a Chip design)都是常用的设计方法。这两种设计方法都旨在将多个

2023-08-24 10:10

芯片验证的工作量约占整个芯片研发的70%,已然成为缩短芯片上市时间的瓶颈。应用OVM方法学搭建SoC设计中的DMA IP验证平台,可有效提高验证效率。

2012-06-20 09:03

在对zynq进行Linux驱动开发时,除了需要针对zynq内ARM自带的控制器适配驱动外,还需要对zynq PL部分的IP核进行驱动开发。对于ARM来说,zynq PL部分的I

2018-06-30 15:10

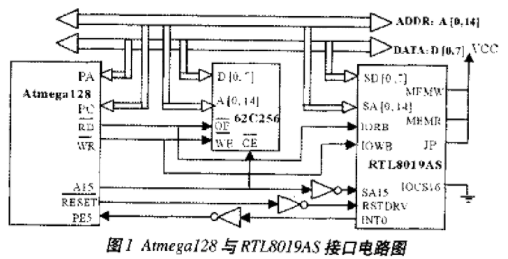

对于嵌入式系统而言,考虑到TCP/IP协议的复杂性以及嵌入式系统自身资源的有限,对TCP/IP的实现并不是一件容易的事情。在一些特殊场合,比如要求实时性或者数据的安全性,实现TCP/IP协议时还需要特别加以考虑。下面

2021-05-26 09:24

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之

2022-04-21 08:58