芯片面积估计就是通过目标工艺的库信息,设计的spec、以往设计的信息及,部分IP的综合报告来统计这主要部分的总面积的过程。

2018-04-25 15:36

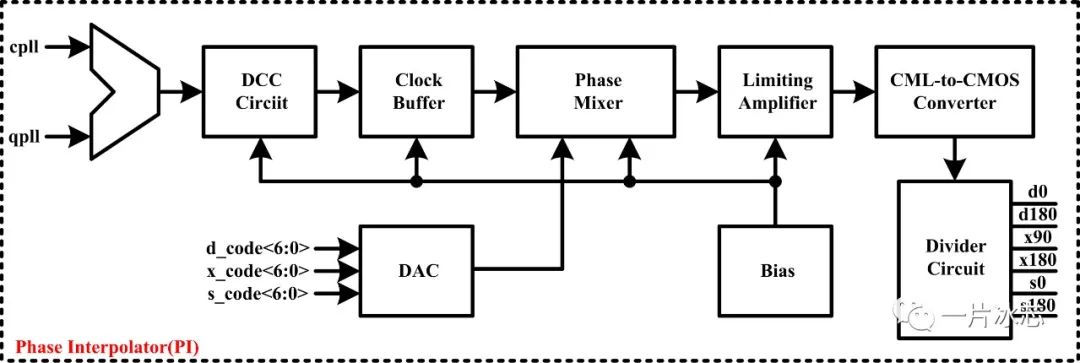

高速SerDes的数据和时钟通路上需要很多buffer,传统CML buffer的有限带宽往往限制系统的奈奎斯特频率

2023-10-31 14:28

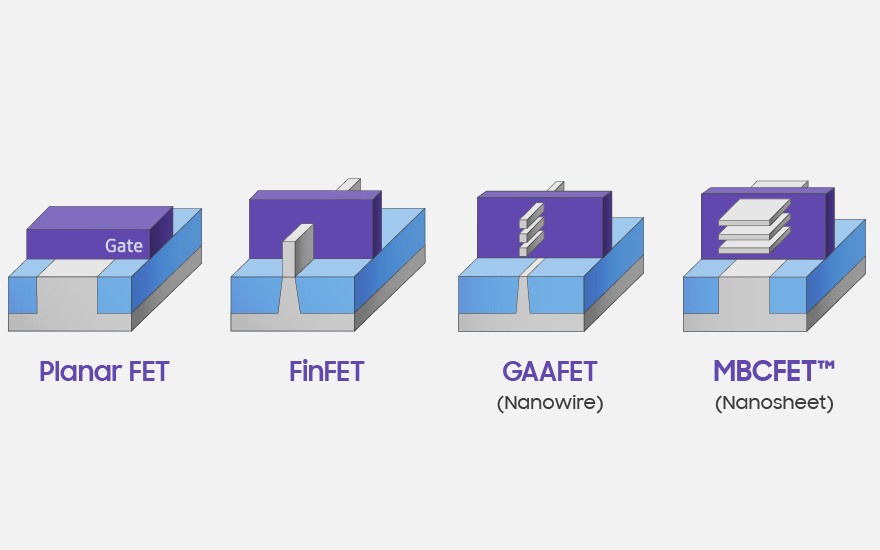

工艺相比,3GAE可将芯片面积减少高达45%,降低50%的功耗或实现35%的性能提升。基于GAA的过程节点有望用于下一代应用,如移动,网络,汽车,AI和物联网。 3GAE的特点是采用GAA的专利变体

2019-05-17 11:29

Navi 48采用自主研发的设计方案,包含有64个计算单元,采用256位显存位宽,显存带宽达到693 GB/s,总带宽高达2770GB/s,而其GPU芯片面积也达到了240mm²。

2024-04-10 16:22

集成电路晶圆代工企业中芯国际集成电路制造有限公司(“中芯国际”)日前宣布,其0.11微米后段铜制程(Cu-BEoL)超高密度IP库解决方案可为客户平均节省31%芯片面积。

2012-03-12 09:14

三星电子副会长李在镕近日参观正在开发“全球第一个3纳米级半导体工艺”的韩国京畿道华城半导体工厂,并听取了关于3纳米工艺技术的报告,他还与三星电子半导体部门社长团讨论了新一代半导体战略。

2020-01-06 10:42

眼下Intel每一代处理器的性能提升被认为是“挤牙膏”,但事实证明该公司的研发能力和脑洞依旧领先,Intel本周二宣布了最新的EMIB技术,旨在解决处理器性能与成本之间的矛盾。

2017-03-29 14:30

华虹半导体最新推出90nm 超低漏电嵌入式闪存工艺平台,助力大容量MCU解决方案 全球领先的特色工艺纯晶圆代工企业华虹半导体有限公司近日宣布,最新推出 90纳米超低漏电(Ultra-Low-Leakage,ULL)嵌入式闪存(eFlash)和电可擦可编程只读存储器(EEPROM)工艺平台,满足大容量微控制器(MCU)的需求。该工艺平台作为华虹半导体 0.11微米超低漏电技术的延续,以更低的功耗和成本为客户提供具有竞争力的差异化解决方案,适用于物联网、可穿戴式设备、工业

2020-10-22 16:46

Speedcore嵌入式FPGA(eFPGA)IP产品可以被嵌入到一款ASIC或者SoC之中,客户通过细化其所需的逻辑功能、RAM存储器和DSP资源,然后Achronix将配置Speedcore IP以满足其个性化的需求。Speedcore查找表(LUT)、RAM单元、DSP64单元和定制单元块能够以灵活的纵列方式组合在一起,为客户的应用创建最优化的可编程功能。

2017-10-18 15:26

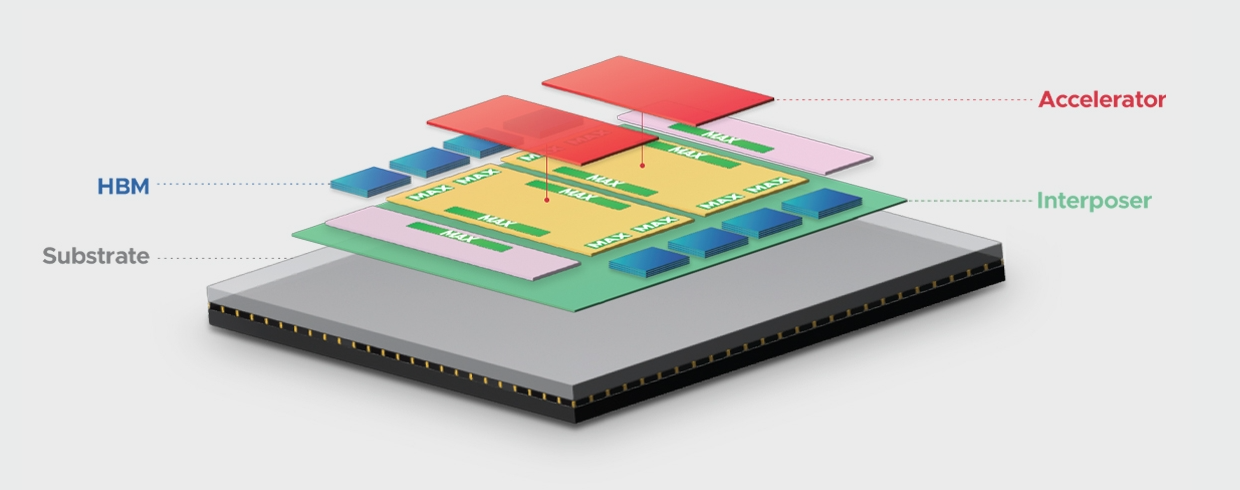

电子发烧友网报道(文/梁浩斌)博通最近推出了3.5D XDSiP的芯片封装平台技术,面向下一代高性能AI、HPC应用的定制XPU和ASIC。3.5D XDSiP的最大亮点,在于可以将超过6000

2024-12-10 09:15