芯片面积估计就是通过目标工艺的库信息,设计的spec、以往设计的信息及,部分IP的综合报告来统计这主要部分的总面积的过程。

2018-04-25 15:36

Speedcore嵌入式FPGA(eFPGA)IP产品可以被嵌入到一款ASIC或者SoC之中,客户通过细化其所需的逻辑功能、RAM存储器和DSP资源,然后Achronix将配置Speedcore IP以满足其个性化的需求。Speedcore查找表(LUT)、RAM单元、DSP64单元和定制单元块能够以灵活的纵列方式组合在一起,为客户的应用创建最优化的可编程功能。

2017-10-18 15:26

CSP封装是最新一代的内存芯片封装技术,其技术性能又有了新的提升。CSP封装可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况,绝对尺寸也仅有32平方毫米,约为普通的BGA

2019-06-24 14:12

随着深亚微米CMOS工艺的发展,尺寸按比例不断缩小,对芯片面积的挑战越来越严重,双极型晶体管以及高精度电阻所占用的面积则成为一个非常严重的问题。鉴于此,本文提出了一款高精度的基准电压源的设计方案,经证实,该电路具备占用芯片面

2014-03-10 11:16

当SoC上有超过80%的芯片面积被各种形式的存储器占用之时,存储器的DFT测试已经变得非常重要。

2023-12-09 09:56

通过在各处合理地增加晶体管,堪萨斯分校的工作人员构造了与门、或门和异或门,以及执行进位功能的电路。这4种电路比相应的互补金属氧化物半导体(CMOS)电路使用更少的晶体管,芯片面积也小得多。

2018-03-23 16:17

要求同时具备设计面积最小、运行频率最高是不现实的。更科学的设计目标应该是在满足设计时序要求(包括对设计频率要求)的前提下,占用最小的芯片面积。或者在所规定的面积下,使设计的时序余量更大、频率跑得更高。这两种目标充分体

2022-04-15 16:59

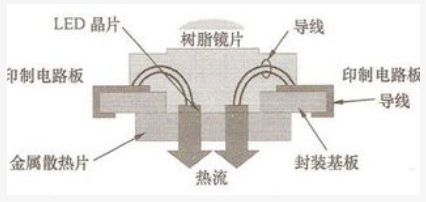

并非进行芯片表面改善后,再加上增加芯片面积就绝对可以迅速提升亮度,因为当光从芯片内部向外扩散射时,芯片中这些改善的部分无法进行反射,所以在取光上会受到一点限制,根据计算

2019-09-19 16:49

HMC560A 芯片是砷化镓 (GaAs)、单片微波集成电路 (MMIC)、双平衡混频器,可以在较小的芯片面积内用作 24 GHz至38 GHz 的上变频器或下变频器。此混频器无需外部元件或匹配电路。

2025-03-26 10:09

Imagination公司日前基于其神经网络加速器(NNA)架构PowerVR 2NX推出了两款全新的神经网络内核AX2185和AX2145,其设计目的是在极小芯片面积上以极低功耗实现神经网络高性能计算。

2018-06-20 10:50