半导体芯片易受大电流与高电压现象影响。为实现元件级保护,我们采用片上ESD保护电路来提供安全的静电放电电流泄放路径。静电放电(ESD)是电子设备面临的常见威胁。当ESD

2025-05-13 11:21 深圳市浮思特科技有限公司 企业号

在亚微米以下的电路设计中,需要对电路进行全芯片的ESD保护结构的设计。如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为全

2012-04-23 10:17

ESD试验作为EMC测试标准的一项基本测试项目,如果产品的前期设计考虑不足,加上经验不够的话,往往会让人焦头烂额。一般中小型企业,如果没有专门的EMC工程师,往往这项工作就必须由硬件工程师来承担。对于整机来说,ESD抗扰能力不仅仅来自

2019-01-01 09:18

承担。对于整机来说,ESD抗扰能力不仅仅来自芯片的ESD耐压,PCB的布局布线,甚至与工艺结构也有密切关系。

2016-11-04 19:33

为实现十倍于USB2.0的传输速度,USB 3.0控制芯片必须使用更先进的制程来设计与制造,但这也造成USB 3.0的控制芯片对ESD的耐受能力快速下降。除此之外,USB 3.0会被大量用来传输影音

2019-01-18 14:33

ESDi平台是一款先进的芯片级ESD(静电防护)验证平台,为设计流程的各个阶段提供定制化解决方案。该平台包括原理图级HBM(人体模型)检查工具ESDi-SC,

2025-04-22 10:25

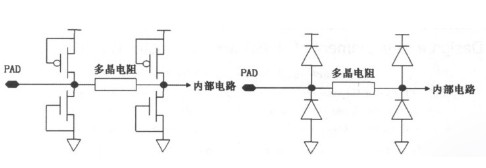

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将

2019-03-04 14:24

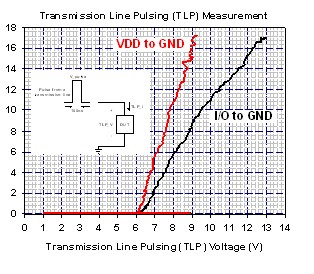

目前几乎所有的芯片组都有片上ESD保护。ESD电路放在芯片的外围和邻近I/O焊垫处,它用于在晶圆制造和后端装配流程中保护芯片

2018-06-05 07:34

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,

2014-12-24 11:05