当SoC上有超过80%的芯片面积被各种形式的存储器占用之时,存储器的DFT测试已经变得非常重要。

2023-12-09 09:56

DFT 可以降低通过问题器件的风险,如果最终在实际应用中才发现器件有缺陷,所产生的成本将远远高于在制造阶段发现的成本。它还能避免剔除无缺陷器件,从而提高良率。插入 DFT 亦能缩短与测试开发相关的时间,并减少测试装配好的芯片

2019-09-16 14:31

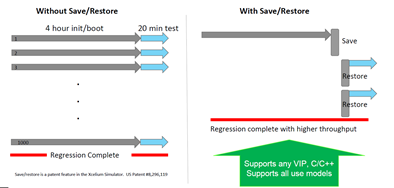

当今片上系统的设计复杂性日益增加,可能导致长达数小时、数天甚至数周的可测试性 (DFT) 仿真设计。由于这些往往发生在专用集成电路(ASIC)项目结束时,当工程变更单(ECO)强制重新运行这些长时间

2023-04-20 10:21

在芯片设计的世界里,有一种被称为"火眼金睛"的技术,它就是DFT(Design for Testability,可测性设计)。今天,就让我们一起揭开这项技术的神秘面纱,看看它是如何成为芯片质量的守

2025-03-01 09:49

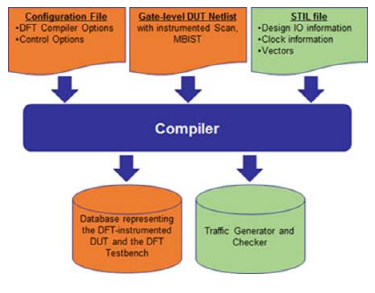

对于许多现有的和未来的集成芯片器件来说,一项主要挑战就是如何为庞大数量的设计创建测试图案。对于有百万门甚至数亿门的设计,传统上等到设计完成再创建测试图案的方法是不切实际的,产生所有这些图案需要庞大

2018-01-31 07:06

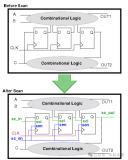

Ad-hoc DFT 包括一套提倡“良好”设计规范的规则,旨在简化和加速测试流程。例如,提供置位和复位信号,使得所有触发器均可初始化;避免引起振荡的异步逻辑反馈;逻辑门设计应注意避免扇入数过大(扇入

2018-04-12 14:29

滑动DFT的推导是相当简单的,并且和DFT完全等价。也就是说,滑动DFT算法相比传统DFT或FFT算法没有信息丢失或失真。下面有完整的推导过程,没有兴趣的读者可以跳过这

2018-02-19 01:01

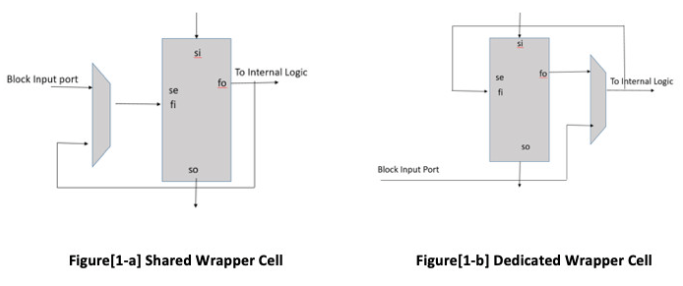

香山处理器的第二代微架构,南湖微架构,引入了L3 Cache,可配置多核形态,我们完成流片的是双核版本的南湖。较第一代雁栖湖,设计规模在大幅膨胀,主频也从1.3GHz提升到2GHz。规模化之后对DFT设计及物理实现都造成新的挑战,我们的设计方法学也需要与时俱进。

2022-12-14 10:51

高级测试设计 (DFT) 技术通过提高顺序翻牌的可控性和可观察性,提供高效的测试解决方案,以应对更高测试成本、更高功耗、测试面积和较低几何尺寸下的引脚数。这反过来又提高了SoC的良率,可靠性和可测试性是当今ASIC世界的重要因素。

2022-11-23 14:53