sign-off,写出SDF3.0用以后仿真,搭建后仿真的验证环境,添加sc/io/macro的verilog model,仿真输出VCD给Redhawk/Voltus

2024-10-23 09:50

我们知道芯片上电后,没有POR复位的或者不带复位的寄存器q端要么处于1,要么处于0状态,对于仿真机器而言就是x态。

2024-02-29 10:51

FPGA的前仿真和后仿真在芯片设计和验证过程中扮演着不同的角色,各自具有独特的特点和重要性。

2024-03-15 15:29

单击快捷图标栏的齿轮图标启动仿真,仿真完毕后,参考前文的前仿真中回波损耗和TDR阻抗曲线图提取方法提取后

2019-02-02 16:32

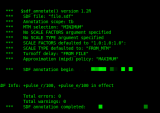

SDF文件是在VCS/NC-Verilog后仿真运行时将STD/IO/Macro门级verilog中specify的延迟信息替换为QRC/Star-RC抽取的实际物理延时信息,所以如果SDF文件

2023-12-18 09:56

Keil 官方仿真器 ULINKPro 仿真器支持的芯片型号如下,ULINKpro的详细介绍请参考产品中心 ULINKPro 介绍。

2019-11-22 09:52

相对于RTL仿真,门级仿真占用的计算资源虽然很多,但是在静态时序检查(STA)工具普遍应用之前,带时序的动态门级仿真几乎可以说是唯一的timing sign-off手段了。

2023-06-08 10:07

接着上文,MCU芯片设计了mbist、scan chain之后,功能仿真失败?

2023-02-20 09:35

在进行数字电路后仿真时,经常会遇到很多时序为例,通常这些违例都是由网表中大量的时序检查报出的。

2024-01-03 09:43

在默认的headset工程中,当系统进行关机的时候,会让芯片进入到dormant状态,本文介绍如何在关机后让芯片进入到Off状态。

2023-10-25 09:29