室温超导是否可以帮助降低芯片功耗

2023-08-25 10:01

前段时间,和几个业界同仁在探讨如何降低PUE,引发了对冷热通道温升、风机功率、自然冷源利用的相关探讨,发现讨论PUE居多,但降低PUE对IT设备的功耗的影响关注较少。本文结合环境温度对服务器芯片功耗的影响来探讨数据中

2022-10-24 11:29

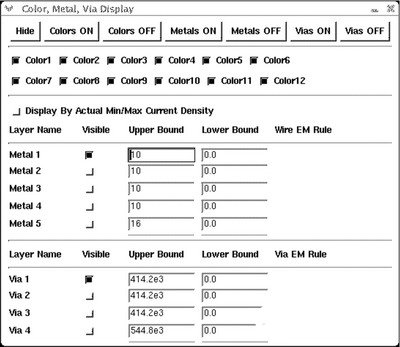

Redhawk 能在项目设计早期 (只是做了place和cts 之后)分析出P/G 结构上的问题,分析P/G structure 不需要STA 和SPEF 文件。 这里就是 P/G weakness 分析有两种方式来报出这些连接有问题的P/G连接。

2023-12-07 10:21

为了查看power grid 有问题的区域,可以在GUI里高亮这些有较弱连接的instance,需要结合之前提到的resistance report: 1)如下这个命令是高亮和VDD 连接较弱的instance。

2023-12-07 10:18

这种模型是Synopsys提出的。提高了精确度。driver model变成了一个非线性的符合电流源,电流随电压和时间变化。receiver model变成了两个电容的并联。

2024-01-10 16:06

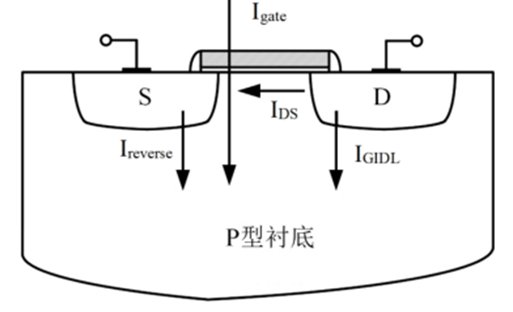

静态功耗(漏电功耗)是指芯片待机状态下所产生的的功率消耗,来源于MOS管内部的泄漏电流;泄漏电流有多个组成部分

2023-12-01 14:25

不同低功耗技术的EDA支持是支离破碎的,结果设计师不得不通过一系列特殊手段定义低功耗功能。更重要的是,设计的可预测性和验证变得极其困难。同时,由于设计上的复杂度以及以前缺乏EDA自动化手段的原因,工程设计团队面临着手工分析和运用这些技巧的难题,而且也没把握在不影响

2018-04-13 15:00

第一种方案就是多电源多电压技术,Multi supply Multi Voltage(MSMV)。这是一种可以有效降低动态功耗的技术。芯片可以划分为不同电压域(Voltage Area),也被称为

2018-01-29 10:21

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

2023-11-29 10:19

在本文的FFT芯片中布置有12对电源和地PAD数,故符合要求。在设计中,应该多放置几对电源和地PAD,不但可以减少电压降,冗余的电源、地PAD以及键合线(Bonding Wire)都可以减少寄生电容,从而降低顺势电流变化而导致的电压波动。

2021-03-24 14:05