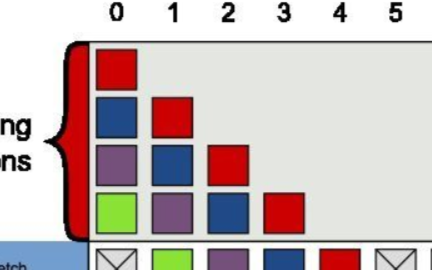

颜色表示了不同阶段的可配置性或可编程性:绿色表示该流水线阶段是完全可编程控制的,黄色表示该流水线阶段可以配置但不是可编程的,蓝色表示该流水线阶段是由GPU固定实现的,开

2018-05-04 09:16

为什么有些CPU的主频更低,但运算效率却更高呢? 比如:51单片机30M主频,STM32单片机20M主频,执行相同一段代码可能主频更低的STM32所花的时间更短。 这里就牵涉到CPU流水线的问题,本文围绕CPU流水线描述相关内容。

2022-10-24 14:34

本文解释了流水线及其对 FPGA 的影响,即延迟、吞吐量、工作频率的变化和资源利用率。

2022-05-07 16:51

stage:和声明式的含义一致,定义流水线的阶段。Stage 块在脚本化流水线语法中是可选的,然而在脚本化流水线中实现 stage 块,可以清楚地在 Jenkins UI 界面中显示每个 stage 的任务子集。

2023-07-20 16:43

如果有数字电路常识的人都知道,利用一块组合逻辑电路去做8位的加法,其速度肯定比做2位的加法慢。因此这里可以采用4级流水线设计,每一级只做两位的加法操作,当流水线一启动后,除第一个加法运算之外,后面每经过一个2位加法器的延时,就会得到一个结果。

2019-02-04 17:20

流水线设计通常可以在一定程度上提升系统的时钟频率,因此常常作为时序性能优化的一种常用技巧。如果某个原本单个时钟周期完成的逻辑功能块可以进一步细分为若干个更小的步骤进行处理,而且整个数据处理过程是单向

2023-05-08 10:55

本文将讨论处理器的一个重要的基础知识:流水线。熟悉计算机体系结构的读者一定知道,言及处理器微架构,几乎必谈其流水线。处理器的流水线结构是处理器微架构最基本的一个要素,犹如汽车底盘对于汽车一般具有基石性的作用,它承载并

2018-04-08 08:16

之前看一篇论文《A Fast Approach for Generating Efficient Parsers on FPGAs》,里面主要讲的是如何将P4的报文解析通过流水线技术映射到FPGA上

2023-04-08 14:15

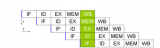

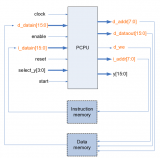

本文实现的CPU是一个五级流水线的精简版CPU(也叫PCPU,即pipeline),包括IF(取指令)、ID(解码)、EX(执行)、MEM(内存操作)、WB(回写)。

2025-04-15 09:46

但在实际应用中,流水线并行并不特别流行,主要原因是模型能否均匀切割,影响了整体计算效率,这就需要算法工程师做手调。因此,今天我们来介绍一种应用最广泛,最易于理解的并行范式:数据并行。

2023-05-26 14:40