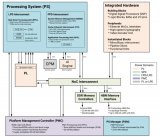

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分,PMC 平台管理控制器,AI Engine 等模块,与以往的 ZYNQ 7000 和 MPSoC 不同,Versal 内部是通过 NoC 片上网络进行互联。

2024-03-06 18:12

ACAP 是一个高度集成的多核异构计算平台,能根据各种应用与工作负载的需求从硬件层对其进行灵活修改。ACAP 可在工作过程中进行动态调节的灵活应变能力,实现了非常强大的性能与性能功耗比

2018-04-09 14:28

对于Versal来说PL(FPGA)开发是至关重要的,这也是Versal比其他ARM的有优势的地方,可以定制化很多ARM端的外设

2024-03-13 15:38

我们从原理图中可以看到 ZYNQ 芯片分为PL和PS,PS端的IO分配相对是固定的,不能任意分配,而且不需要在Vivado软件里分配管脚,虽然本实验仅仅使用了PS,但是还要建立一个Vivado工程,用来配置PS管脚。

2024-04-19 10:45

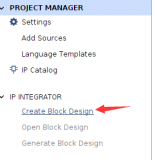

每个工程下面都有一个生成vivado的脚本,用于重建vivado工程,有两种方法可以使用,一是利用批处理文件,右键编辑create_project.bat

2024-03-06 18:10

Versal的DDR4是通过NoC访问,因此需要添加NoC IP进行配置。

2024-03-22 17:18

ALINX黑金7寸LCD屏模块(AN7000)采用IVO的7寸TFT LCD液晶屏, 液晶屏的型号为M070AWAD R0。AN7000 LCD屏模块由TFT 液晶屏和驱动板组成,具体参数可以参考AN7000的用户手册。AN7000实物照片如下:

2024-03-29 16:40

AMD自适应计算加速平台(ACAP)是一个完全软件可编程资源集合,这些资源结合在一起构成片上系统 (SoC),包括以下主要的资源块

2023-11-27 14:12

为了应对无线波束形成、大规模计算和机器学习推断等新一代应用需求的非线性增长,AMD 开发了一项全新的创新处理技术 AI 引擎,片内集成该AI Engine的FPGA系列是Versal™ 自适应计算加速

2024-04-09 15:14

今年3月份,赛灵思(Xilinx)历史上第四位全球CEO Victor Peng 先生在北京正式宣布赛灵思将推出“自适应计算加速平台”ACAP。Victor 表示:“作为可以和CPU、GPU

2018-10-05 09:04