Modbus或现场总线的连接端口。每个处理器以及相应的子系统都需要唯一的与其他时钟无关联的频率和类型,因此,它们需要自己的时钟信号。设计一个能产生这些彼此不同、具有所需精度性能的

2020-03-12 10:44

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换

2020-11-22 11:34

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能

2023-04-11 11:06

这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43

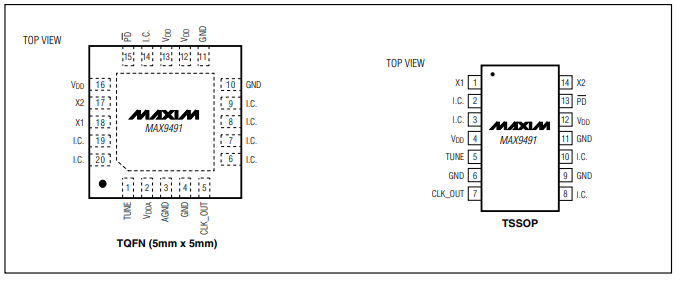

MAX9491是多时钟发生器,非常适合通信应用。该器件提供工厂编程PLL输出,可调节到4MHz至200MHz之间的任意频率。MAX9491使用一次性可编程(OTP) ROM设置PLL输出

2025-04-27 09:57

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。

2019-08-07 17:51

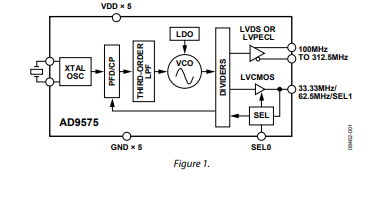

AD9575是一款高度集成的双路输出时钟发生器,包括一个针对网络定时而优化的片内PLL内核。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现线路卡的较高性能。对相位噪声和抖动要求苛刻的其它应用也能受益于该器件。

2025-04-10 17:00

所有的数字电路都需要依靠时钟信号来使组件的运作同步,每单位时间内电路可运作的次数取决于时钟的频率,因此时钟运作的频率即被大家视为系统运作的性能指针。

2018-07-21 10:40

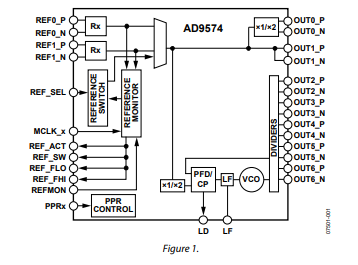

AD9574具有多路输出时钟发生器功能,内置专用锁相环(PLL)内核,针对以太网和千兆以太网线路卡应用进行了优化。 整数N PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现高的网络性能。 AD9574还适合要求低相位噪声和抖动性能的其他应用。

2025-04-10 10:43