继续上文GPGPU体系结构优化方向 [上],介绍提高并行度和优化流水线的方向。

2024-10-09 10:03

从来没有基于MOSFET内部的微观结构去考虑驱动电路的设计,导致在实际的应用中,MOSFET产生一定的失效率。本文将讨论这些细节的问题,从而优化MOSFET的驱动性能,提高整个系统的可靠性。

2021-03-07 10:47

GPU Warp内,32个线程(NVIDIA)锁步lock step执行时,如果遇到每个分支走上了不同分支,比如20个线程if,12个执行else,那么20个线程会先执行,mask调另外的12个。20个线程执行到分支合并点之后,另外12个再执行,直到这12个线程也进行到分支合并点。

2024-04-09 11:30

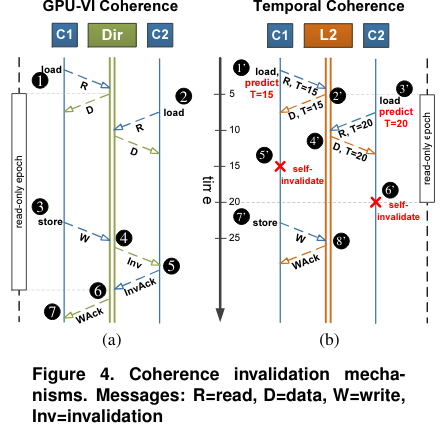

目前的GPU缺乏cache一致性,需要diable 线程private的L1 cache,或者采用基于软件的bulk coherence决策(比如在同步点,flush掉所有的private L1 cache。

2024-10-09 10:06

本文通过对高速BGA封装与PCB差分互连结构的优化设计,利用CST全波电磁场仿真软件进行3D建模,分别研究了差分布线方式、信号布局方式、信号孔/地孔比、布线层与过孔残桩这四个方面对高速差分信号传输性能和串扰的具体影响。

2019-05-29 15:14

完善的项目前期工作预示着更少的项目后期风险,这也是CAE工作的重要意义之一。在整机开发的前期(概念设计和布置设计阶段),由于没有成熟样机进行NVH试验,很难通过试验的方法预测产品的NVH水平。因此,通过仿真的方法对整机NVH性能进行分析甚至优化显得十分重要。

2020-04-06 11:29

为了适应高速信号传输,芯片多采用差分信号传输方式。随着芯片I/O 引脚数量越来越多,BGA焊点间距越来越小,由焊点、过孔以及印制线构成的差分互连结构所产生的寄生效应将导致衰减、串扰等一系列信号完整性问题,这对高速互连设计提出了严峻挑战。

2023-09-28 17:28

很多人都说,高速电路看着比普通的电路的电路结构简单,但是为什么都说很难,说这话的工程师可能还没有深入的了解高速电路的特点。没错,在做低速电路的时候,总想着要做电路匹配等等,高速电路相对来讲确实简单,不是两颗芯片中间加两颗AC耦合电容直接相连,就是一颗芯片与连接器中间加两颗AC耦合电容直接相连。

2018-05-28 10:55

随着计算机网络技术和电子信息技术的迅猛发展,Internet的普及,接入Internet的非PC设备越来越多,各类电子设备像Web个人数字助理、Web可视电话、TV机顶盒接入Internet的需求也越来越大,嵌入式TCP/IP的Internet网络化将成为网络发展的趋势。

2019-02-16 11:24

选择Simulator → BDF → BDF,在界面中设置参数。在Basic Settings界面中的Calculation Type选择TDDFT-OPT+Freq,方法采用默认的PBE0泛函,基组在Basis中的All Electron类型中,选择Def2-SVP。

2022-11-03 11:18