电子发烧友

9642次浏览

本文开始介绍了累加器的概念和相位累加器原理,其次介绍了累加器的作用,最后介绍了流水线相位累加器的设计与累加定时器在PLC

2018-04-11 11:40

相位累加器一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。DDS 正是利用了这一特点来产生正弦信号。如图 2,根据

2009-09-03 08:43

在中央处理器中,累加器(accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器

2018-04-11 16:46

累加器使用的注意点及自定义累加器

2020-04-02 09:31

标题中所提到的DDS,我感觉这两个放一起也可以,因为DDS的核心思想就是使用的相位累加器。那么这玩意儿的作用是啥?简单来说就是在FPGA工作主频之下,可以生成任意频率的周期信号出来。

2025-05-16 13:56

本文首先对寄存器、累加器、暂存器做个哥介绍,其次解答了累加器是不是寄存器,最后阐述了寄存

2018-04-11 16:31

怎么由布尔控件控制开始和停止累加器的运行

2019-06-04 22:09

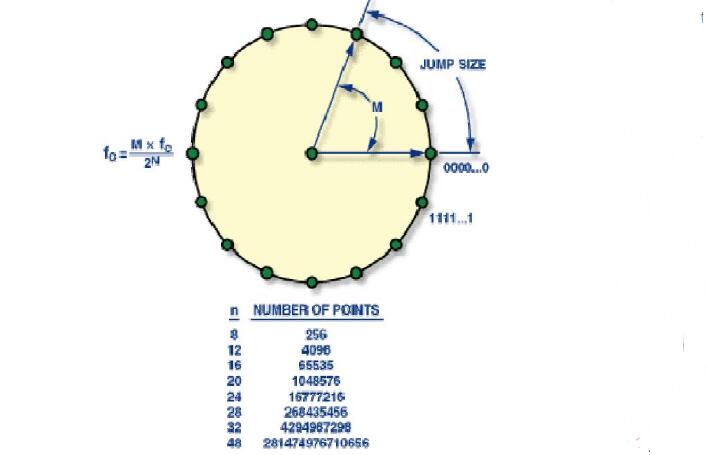

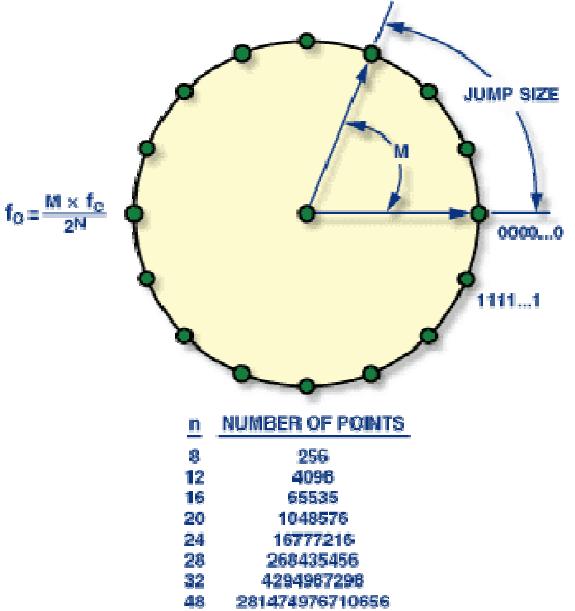

假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N, 则可以产生一个频率为Fc/2N 的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,

2019-07-22 08:52

刚刚接触FPGA,编程方面也不是很擅长。今天做了一个累加器的verilog编程,仿真波形图一直出错,想请大神指教一下错误的原因,十分感谢!我要实现的累加器功能是:连续输入几百个gary_value

2015-05-23 20:09

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。 1、DDS相位累加器 (1)DDS合成流程 首先讲述DSS(直接频率合成法)的原理。 DDS是重要的频率合成方法,在波形

2020-11-29 10:19