本文开始介绍了累加器的概念和相位累加器原理,其次介绍了累加器的作用,最后介绍了流水线相位累加器的设计与累加定时器在PLC

2018-04-11 11:40

Invt英威騰変頻故障代碼

2018-10-06 16:45

自昊芯推出专题讲解SCI串口通讯奇偶校验,分为两期讲解,上期主要讲解标准SCI模式下的奇偶校验,本期主要讲解增强FIFO模式下的奇偶校验。

2022-11-02 09:30

奇偶校验是一种简单、实现代价小的检错方式,常用在数据传输过程中。对于一组并行传输的数据(通常为8比特),可以计算岀它们的奇偶校验位并与其一起传输。接收端根据接收的数据重新计算其

2023-09-05 10:40

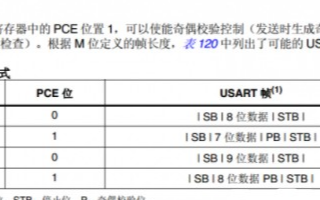

stm32 usart奇偶校验如何配置?或许你在stm32 usart奇偶校验过程中会遇到如下一些坑,stm32 usart偶校验错误标志位以及出现偶校验错误,奇偶校验位包含在数据位中等等这些可能是你将错误的数据放到

2021-07-23 09:55

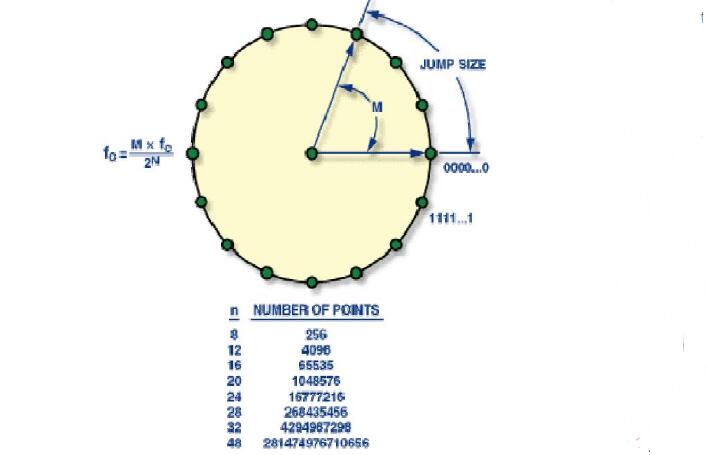

在中央处理器中,累加器(accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写回到内存,也许马上就得读回来。然而存取主存的速度是比从算术逻辑单元到有直接路径的

2018-04-11 16:46

本文针对k-medoids算法具有初始点选取复杂、聚类迭代时间久、中心点选取消耗资源过多等缺点,使用Hadoop平台下的MapReduce编程框架对算法进行初始点的点密度计算选取并行化、非中心点分配

2018-05-18 09:06

STM32串口通信使用奇偶校验的时候应该设置数据位长度9bit,奇偶校验是硬件完成的,并且stm32用校验位时,数据位要选9位,8位会出现故障可能。

2021-07-23 09:26

基于串行异步收发器(UART)的通信中经常用到循环冗余校验(CRC),常见的CRC校验电路多为串行校验,校验所需时钟周期较多,基于查找表或输入矩阵转换的并行算法,需要存储余数表,占用大量的硬件资源

2017-11-18 11:24

算法之空间复杂度:衡量一个算法运行需要开辟的额外空间

2022-08-31 10:29