“ 光刻作为半导体中的关键工艺,其中包括3大步骤的工艺:涂胶、曝光、显影。三个步骤有一个异常,整个光刻工艺都需要返工处理,因此现场异常的处理显得尤为关键”

2024-10-22 13:52

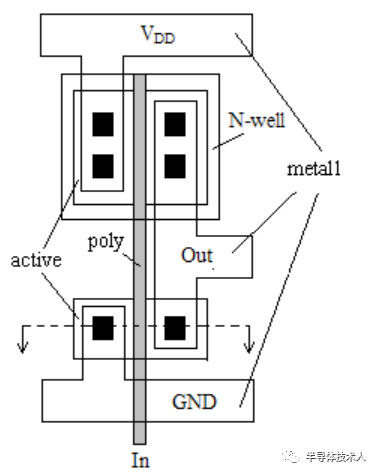

CMOS 集成电路的基础工艺之一就是双阱工艺,它包括两个区域,即n-MOS和p-MOS 有源区

2022-11-14 09:34

当栅与衬底之间存在压差时,它们之间存在电场,静电边界条件使多晶硅靠近氧化层界面附近的能带发生弯曲,并且电荷耗尽,从而形成多晶硅栅耗尽区。该耗尽区会在多晶硅栅与栅氧化层之间产生一个额外的串联电容。当栅氧化层厚度减小到 2nm 以下,此电容的影响也会变得越来越严重,已

2024-08-02 09:14

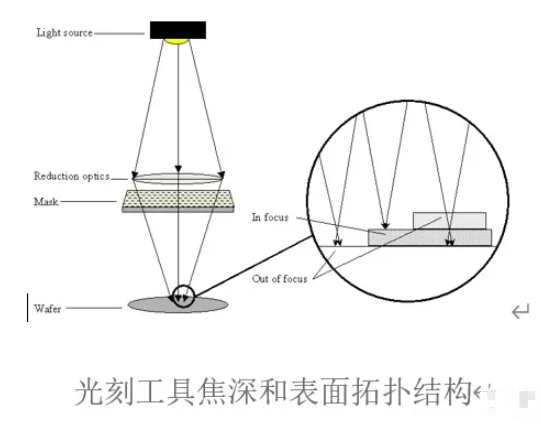

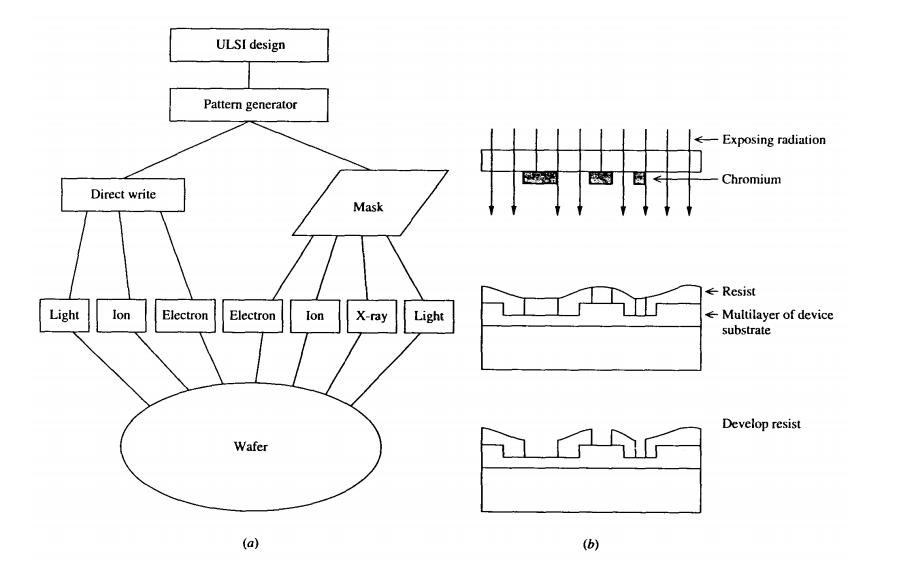

通常,光刻是作为特性良好的模块的一部分执行的,其中包括晶圆表面制备、光刻胶沉积、掩模和晶圆的对准、曝光、显影和适当的抗蚀剂调节。光刻工艺步骤需要按顺序进行表征,以确保模

2023-06-02 16:30

在集成电路的制造过程中,有一个重要的环节光刻,正因为有了它,我们才能在微小的芯片上实现功能。 根据维基百科的定义,光刻是半导体器件制造工艺中的一个重要步骤,该步骤利用曝

2020-11-11 10:14

多晶硅栅光刻工艺使用的光刻机是同一技术代集成电路工艺线中最先进、最昂贵的设备,它采用 UV 光源进行曝光,波长从g线(436nm)到DUV(248pm 和 193nm),以及 193nm 浸没式;在

2022-11-17 10:07

CMOS工艺是在PMOS和NMOS工艺基础上发展起来的。

2023-07-06 14:25

传统的光刻工艺是相对目前已经或尚未应用于集成电路产业的先进光刻工艺而言的,普遍认为 193nm 波长的 ArF 深紫外光刻工艺是分水岭(见下表)。这是因为 193nm 的光刻

2022-10-18 11:20

CMOS 集成电路的基础工艺之一就是双阱工艺,它包括两个区域,即n-MOS和p-MOS 有源区,分別对应p阱和N

2022-11-14 09:32

光刻技术是将掩模中的几何形状的图案转移到覆盖在半导体晶片表面的薄层辐射敏感材料(称为抗蚀剂)上的过程

2023-04-25 09:55