短沟道效应严重制约了硅基晶体管尺寸的进一步缩小,限制了其在先进节点集成电路中的应用。开发新材料和新技术对于维系摩尔定律的延续具有重要意义。

2024-12-06 11:02

源漏扩展结构(Source/Drain Extension,SDE)在控制 MOS 器件的短沟道效应中起到重要作用。SDE(源漏扩展结构)引入了一个浅的源漏扩展区,以连接沟道和源漏区域。结深的微缩

2025-05-27 12:01

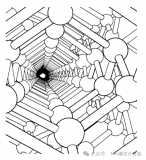

什么是沟道效应? 沟道效应是指在晶体材料中,注入的离子沿着晶体原子排列较为稀疏的方向穿透得比预期更深的现象。

2024-02-21 10:19

为了有效抑制短沟道效应,提高栅控能力,随着MOS结构的尺寸不断降低,就需要相对应的提高栅电极电容。提高电容的一个办法是通过降低栅氧化层的厚度来达到这一目的。栅氧厚度必须随着沟道长度的降低而近似

2025-05-26 10:02

1 深亚微米 BiCMOS[B] 技术 器件进入深亚微米特征尺寸,为了抑制 MOS 穿通电流和减小短沟道效应,深亚微米制造工艺提出如下严格的要求: (1)高质量栅氧化膜。栅氧化膜厚度

2018-03-16 10:29

短沟道效应),芯片的集成度和功耗面临着极大的挑战[1-2]。多值逻辑作为高信息密度集成电路的主要理论基础,为解决这一问题提供了新的方案[3]。在传统的数字电路中最常用的是二值逻辑,而二值逻辑的信息携带

2018-06-14 15:24

随着集成电路工艺技术的不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,集成电路器件的特征尺寸不断按比例缩小,工作电压不断降低。为了有效抑制短沟道效应,除了源漏的结深不断降低

2024-08-02 15:37

随着集成电路工艺技术不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,集成电路器件的特征尺寸不断按比例缩小,工作电压不断降低。为了有效抑制短沟道效应,除了源漏的结深不断降低

2024-01-19 10:01

隧道效应,又称沟道效应,对晶圆进行离子注入时,当注入离子的方向与晶圆的某个晶向平行时,其运动轨迹将不再是无规则的碰撞,而是将沿沟道(原子之间的缝隙)运动并且很少受到原子核的碰撞

2024-01-08 10:25

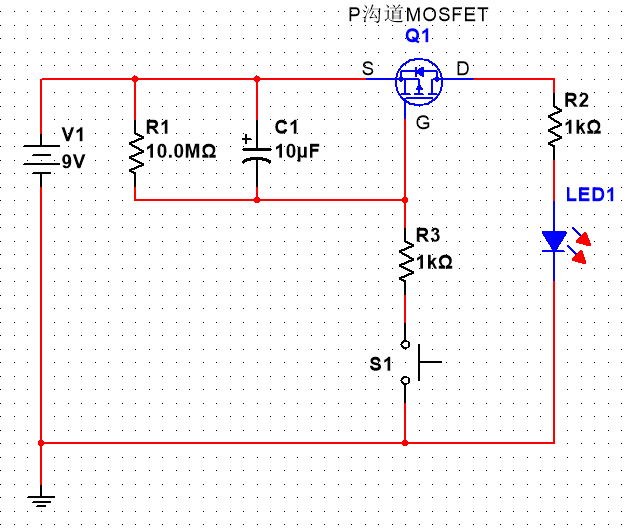

下图是一个由 RC 电路和 P 沟道场效应管组成的延时关机电路。

2023-02-15 11:06