电子发烧友

9312次浏览

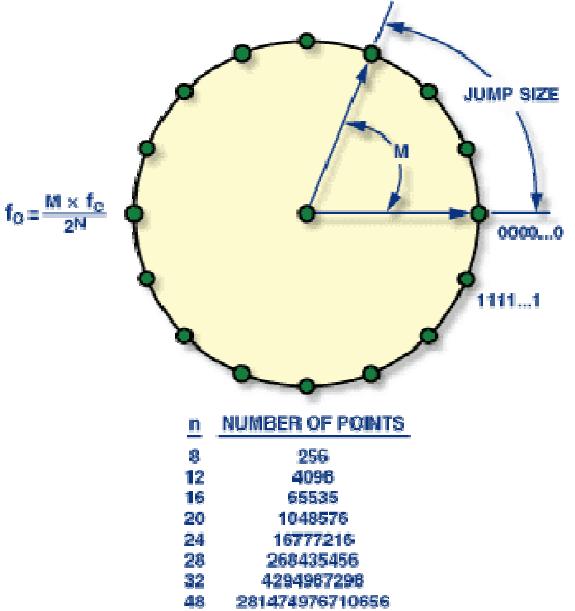

相位累加器一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。DDS 正是利用了这一特点来产生正弦信号。如图 2,根据

2009-09-03 08:43

标题中所提到的DDS,我感觉这两个放一起也可以,因为DDS的核心思想就是使用的相位累加器。那么这玩意儿的作用是啥?简单来说就是在FPGA工作主频之下,可以生成任意频率的周期信号出来。

2025-05-16 13:56

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。 1、DDS相位累加器 (1)DDS合成流程 首先讲述DSS(直接频率合成法)的原理。 DDS是重要的频率合成方法,在波形

2020-11-29 10:19

设计时没有加入溢出清零的进程。频率累加字不断累加到最后应该是大于2的n方减1,溢出后应该要清零重新加吧。可是我没有加入这个进程,modelsim仿出的波形毫无问题。请问这是为什么呢?难道不要清零吗?可这样加下去不会超出量程,越来越大?

2014-06-30 22:14

用流水线技术设计相位累加器,时序上可以工作在更高工作频率,但需要n个周期才能到达反馈(假设是n级流水线),也就是说实际相位输出频率是clk/n ,还是没有提高采样频率不是吗,怎么改进呢

2019-04-21 22:58

假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N, 则可以产生一个频率为Fc/2N 的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,

2019-07-22 08:52

例如,clock=70Mhz, 累加器为16-bit,频率控制字为4096,按公式计算,f0=4096/2^16 * 70 = 4.375MHz。正弦表为256个点的正弦表问题:Q1,相位累加器

2016-03-10 20:10

累加器 (accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写

2020-10-14 16:00

的某种波形。 在测试测量领域有另一个概念 - AWG(任意波形发生器)是跟DDS紧密相关的,波形发生器未必一定采用DDS的方式,但任意波形的产生就离不开DDS了。 DDS可以生成任意波形 - 比如心状波形 DDS的基本原理如下面的框图,主要由以下几个部

2020-09-24 14:20

请问一下AD9910并行端口控制相位时,并行数据是输入到相位累加器中还是输入到相位偏移字中?

2018-12-25 14:02