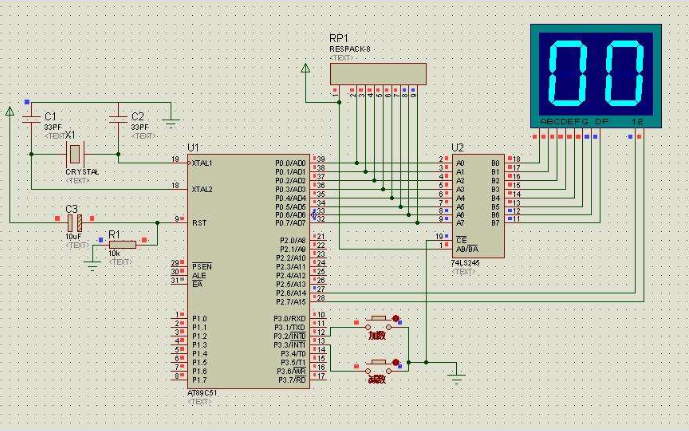

本文档的主要内容详细介绍的是使用计数器中断实现100以内的按键计数的仿真电路图免费下载。

2019-12-26 09:44

100进制计数器 异步级联法组成的100进制计数器 定义集成计数器的高低位,

2008-07-05 14:25

100进制计数器一、 实验目的:1、 熟悉MAX+PLUS环境的基本操作。2、 掌握VHDL和原理图的设计输入方式。3、 设计100

2009-06-28 00:07

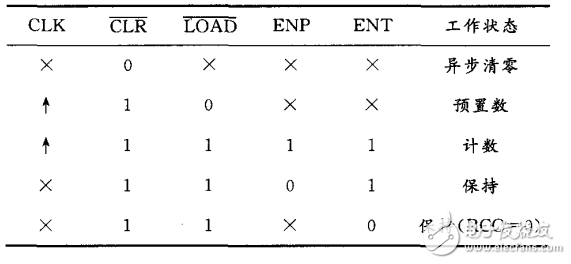

提出一种基于Proteus 软件的任意进制计数器的设计。以74LS163 集成计数器为基础,用置数法设计了两种48 进制计数器,采用Proteus 软件对计数器进行

2016-07-29 18:53

基于8051的Proteus仿真-计数器中断实现100以内的按键计数

2016-09-01 23:35

计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值

2013-07-26 11:38

100进制加减计数器的设计与制作:本电路结构如图袁主要由晶体振荡电路,分频电路,控制

2009-10-22 21:50

计的电路进行仿真实验。仿真结果表明设计的计数器能实现所要求的N进制技术功能。最终得出采用反馈复零法可以实现进制计数器的结

2017-12-21 17:08

产生器做信号源产生所需的时钟脉冲、控制信号,用逻辑分析仪显示时钟脉冲、控制信号及状态输出信号的波形,通过仿真实验可直观描述计数器的工作过程。

2018-01-17 18:19

1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。 2、了解同步

2022-07-10 14:37