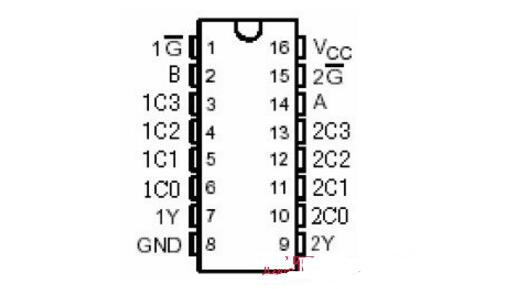

本文介绍了74ls153的管脚图、74ls153功能表、74ls153真值表以及逻辑图,另外还介绍了74ls153封装与74ls

2018-01-26 10:05

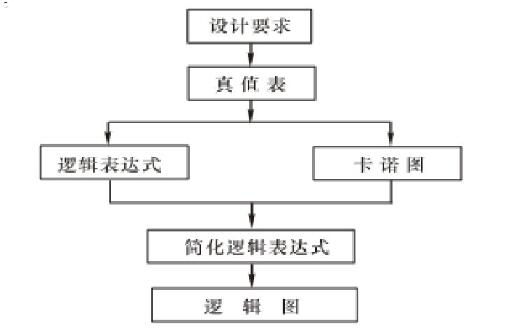

本文介绍了4种方式实现三人表决电路。其中包括用74LS00,74LS20实现三人表决电路、用译码器138和与非门74LS20设计实现三人表决电路、

2018-01-26 17:26

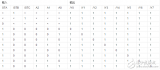

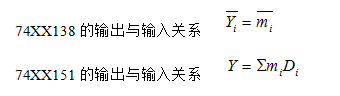

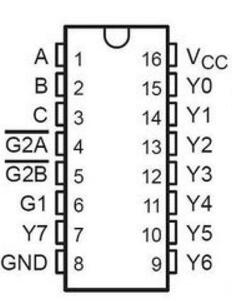

用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/

2017-10-31 15:53

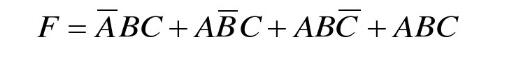

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

2017-10-31 17:15

本文主要介绍了用74ls151实现全加器设计电路。根据全加器的定义可知:输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。输出为:S,Co,其中S为本位和

2018-05-07 09:52

本文主要详解四位全加器74ls83,首先介绍了74ls83特点及引脚图、真值表,其次介绍了74ls83功能表、典型参数及

2018-05-31 09:12

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

2018-07-25 16:03

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位

2021-06-29 09:14

加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位

2018-07-25 11:15

本文主要介绍了数据选择器74ls153应用电路图大全(表决电路\交通灯\报警电路)。所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。1G、2G为两个独立的使能端;B、A为公用的地址

2018-05-07 16:59