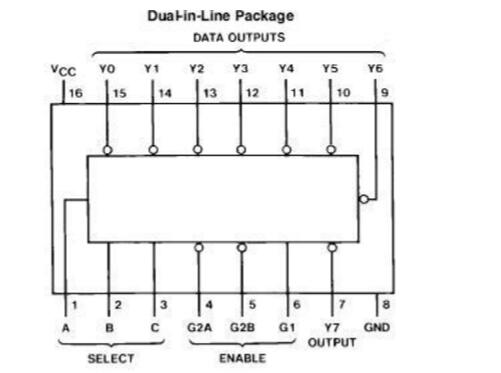

74LS139 为两个2线-4 线译码器,共有 54/74S139和 54/74LS139 两种线路结构型式。可对2位高位地址进行译码,产生4个片选信号,最多可外接4个芯片。本文首先介绍了

2018-05-03 18:35

自昊芯推出专题讲解SCI串口通讯奇偶校验,分为两期讲解,上期主要讲解标准SCI模式下的奇偶校验,本期主要讲解增强FIFO模式下的奇偶校验。

2022-11-02 09:30

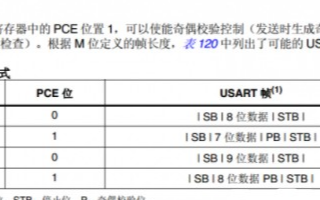

STM32串口通信使用奇偶校验的时候应该设置数据位长度9bit,奇偶校验是硬件完成的,并且stm32用校验位时,数据位要选9位,8位会出现故障可能。

2021-07-23 09:26

stm32 usart奇偶校验如何配置?或许你在stm32 usart奇偶校验过程中会遇到如下一些坑,stm32 usart偶校验错误标志位以及出现偶校验错误,

2021-07-23 09:55

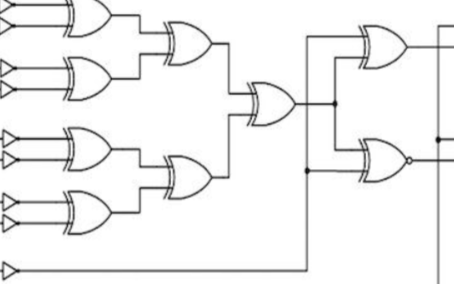

奇偶校验是一种简单、实现代价小的检错方式,常用在数据传输过程中。对于一组并行传输的数据(通常为8比特),可以计算岀它们的奇偶校验位并与其一起传输。接收端根据接收的数据重新计算其

2023-09-05 10:40

本应用笔记实现了一个二进制奇偶校验生成器和校验器,具有两个数据输入变体、一个并行数据输入和一个串行数据输入。它描述了实现的逻辑、GreenPAKs 的

2022-04-27 16:43

模块有标准模式和增强FIFO模式,这两种模式均可通过奇偶校验,校验收发数据的一致性,从而更有效助力于工程师实现高效精准闭环控制,于广泛应用于电动车、电动汽车、轨道交通、全电飞机、新能源发电、机器人等工业自动化高精度控

2022-10-13 11:54

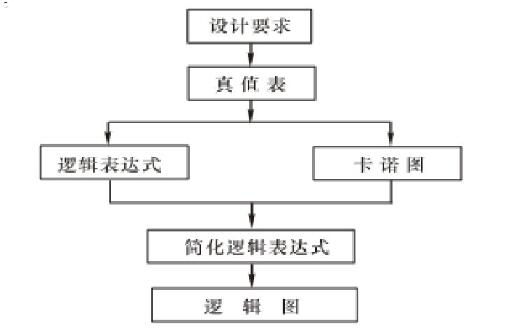

本文介绍了4种方式实现三人表决电路。其中包括用74LS00,74LS20实现三人表决

2018-01-26 17:26

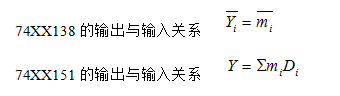

本文主要介绍了用74ls151实现全加器设计电路。根据全加器的定义可知:输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。输出为:S,Co,其中S为本位和

2018-05-07 09:52

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

2017-10-31 17:15