STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01

一、从结构说起: 1、P-bank SDRAM,也即我们的内存,我们的电脑,手机等设备都离不开我们的内存。一个设备运行速度的快慢,内存起到关键性的作用,就像我们的电脑,开机之后一般都是把一些应用程序加载到内存里运行,因为RAM的读写速度要远远大于ROM,而我们的SDRAM,即同步动态随机存储器,就是通过不断地刷新,充电,防止电容电量的丢失,从而保留住数据。与CPU交换数据,根据CPU位宽的不同,要相应选择不同的SDRAM芯片,SDRAM芯片的位宽不等,

2021-03-25 17:08

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30

Boosting是一种用来提高弱分类器准确度的算法,是将“弱学习算法“提升为“强学习算法”的过程,主要思想是“三个臭皮匠顶个诸葛亮”。一般来...

2020-12-10 21:25

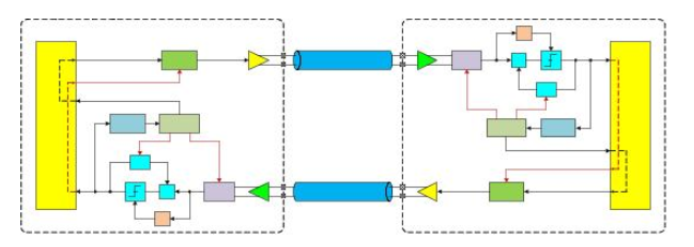

在PCIe 3.0和4.0中的链路均衡技术相较于先前代要复杂得多,这样一种动态均衡技术可以分为两个方面进行讨论。

2020-04-07 11:24

在单处理器(嵌入式MCU)的计算机系统中,在某一具体时刻处理器只能运行一个任务,但是可以通过将处理器运行时间分成小的时间段,多个任务按照一定的原则分享这些时间段的方法

2023-05-08 09:38

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22

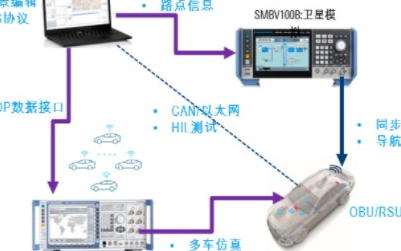

在理论篇,我们介绍了理论上车辆模拟仿真的情况,那么为了实现车载拥塞场景的仿真,我们需要一些相应的测试仪表、仿真平台和测试用例来实现拥塞场景的模拟工作,整个平台的逻辑示意图如图1所示,有如下几个部分组成和相应的功能模块

2022-02-26 09:36

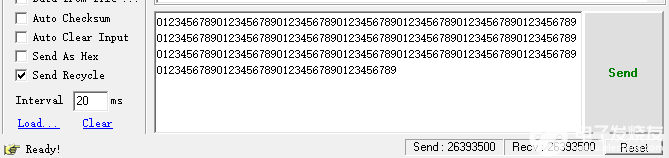

在前一篇文章里,大致提出了我的串口驱动框架理论。里面做了一些对串口驱动特性的幻想。也在 NUC970 芯片下通过了中断模式的实践验证。但是,因为 NUC970 的 uart 自带 fifo 。用它测试效果好,并不能真正说明驱动框架通过验证了。

2022-06-22 09:03

详析三个制造业理论上一节说到如何增加流速v的值来改变Mv的整体数值,从而增加有效产出。这一节主要解析下在广义动量定律下的以改变速度为代表的三个制造业理论,福特的流水线,丰田的LP,高德拉特的瓶颈控制

2023-10-31 14:00 福州基石数据服务股份有限公司 企业号