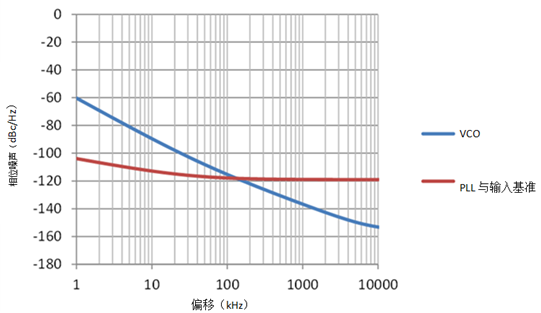

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果B

2016-07-18 14:24

在PLL和VCO频率合成系统中,获得低于5 µs的频率和相位建立时间需极宽的环路带宽。环路带宽(LBW)定义控制环路的速

2016-07-20 16:15

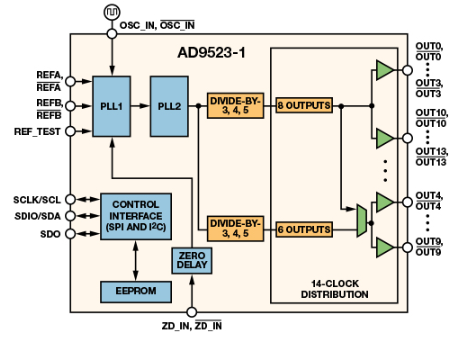

的设计时面临的众多性能瓶颈之一。一个普通系统有几个低频、嘈杂的信号,PLL可以将其上变频到更高的频率,以便为这些器件计时。单个高频PLL可以解决频率转换问题,但很难创建一个环路带宽足够低的PLL来滤除噪声基准电压源的影响。

2023-03-07 13:58

本文针对传统锁相环所存在的锁相范围窄、环路带宽和控制参数固定、以及提高锁相速度与减小稳态误差相互制约等问题,提出了一种新型带宽自适应全数字锁相环的设计方案。该设计方案中的系统采用比例积分控制

2014-01-17 11:33

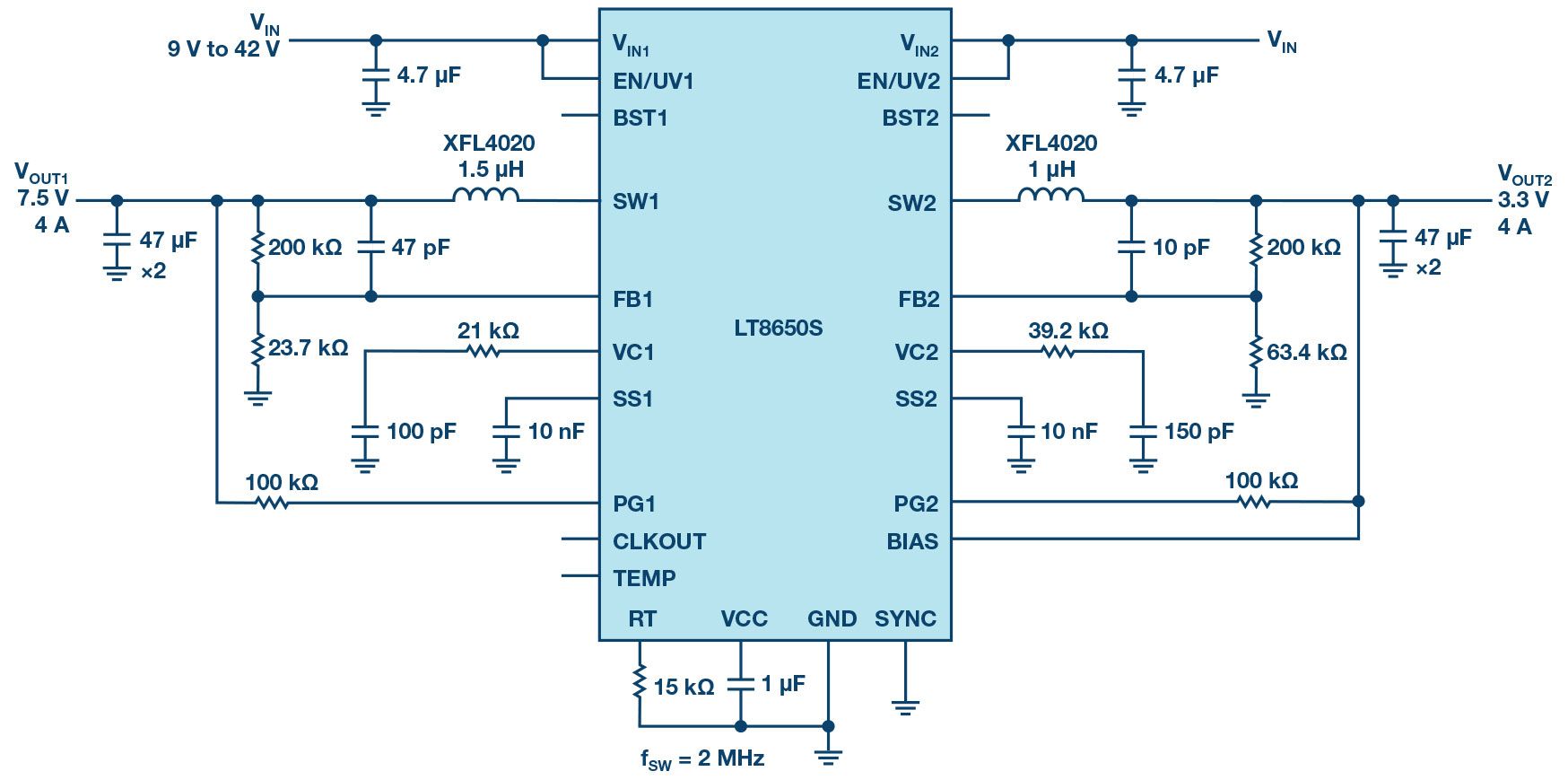

图1所示为旨在优化瞬态响应的一种双路输出稳压器。虽然LT8650S包括内部补偿机制,但仍然采用了外部补偿机制,这是为了尽量减少瞬态响应时间和输出电压偏移。开关频率为2 MHz,因而可以实现更高的环路带宽和更快的瞬态响应。

2023-02-14 10:03

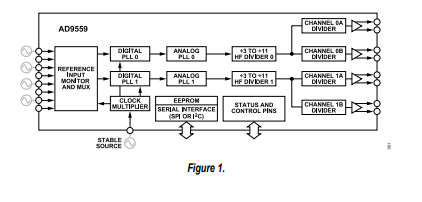

AD9559是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。AD9559产生的输出时钟可以与多达四路外部输入参考时钟同步。DPLL可以

2025-04-10 14:35

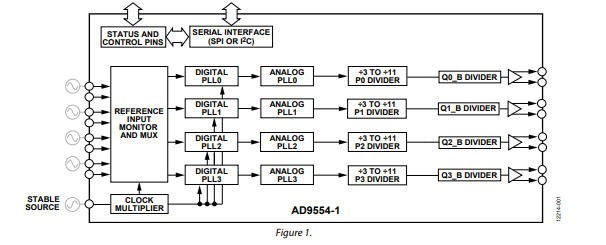

AD9554 是一款低环路带宽时钟转换器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。 AD9554产生的输出时钟可以与多达四路外部输入参考时钟同步。 数字PLL

2025-04-10 11:51

AD9554-1是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。 AD9554-1产生的输出时钟可以与多达四路外部输入参考时钟同步

2025-04-10 11:21

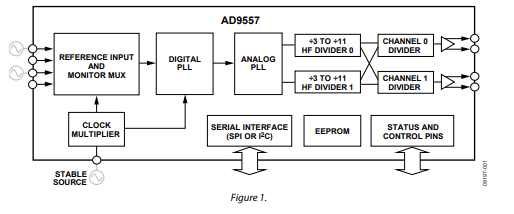

AD9557是一款低环路带宽时钟乘法器,可为包括同步光纤网络(SONET/SDH)在内的许多系统提供抖动清除和同步能力。AD9557可产生与一个或两个外部输入参考时钟同步的输出时钟。数字锁相环

2025-04-10 14:42

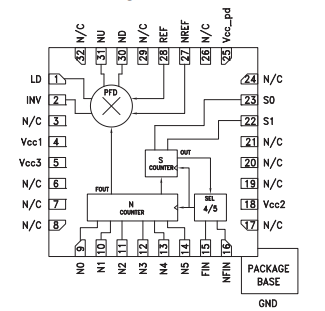

相位噪底性能,HMC698LP5(E)这款频率合成器具有宽环路带宽和低N特性,从而实现快速建立时间和极低相位噪声。 与差分环路滤波器结合使用时,HMC698LP5(E)可用来将VCO相位锁定至参考振荡器。

2025-04-27 17:09