PrimeTime 进行静态时序分析时把整个芯片按照时钟分成许多时序路径。路径的起点是时序单元的输出引脚或是设计的输入端口,路径的终点是时序单元的输入引脚或是设计的输出端口。根据起点和终点的不同,可将逻辑电路分解为图1中用虚线表示的四种路径,分别代表了以下四种类型: 路径1起始于输入端口,终止于时序单元的数据输入端;路径2起始于时序单元的时钟引脚,终止于时序单元的数据输入端;路径3起始于时序单元的时钟引脚,终止于输出端口;路径4起始于输入端口,终止于输出端口。

2018-06-22 14:40

本文章主要详细介绍了pcb版图设计工具,分别有FreePCB、MentorPADS、MentorWG2005。

2019-04-24 17:47

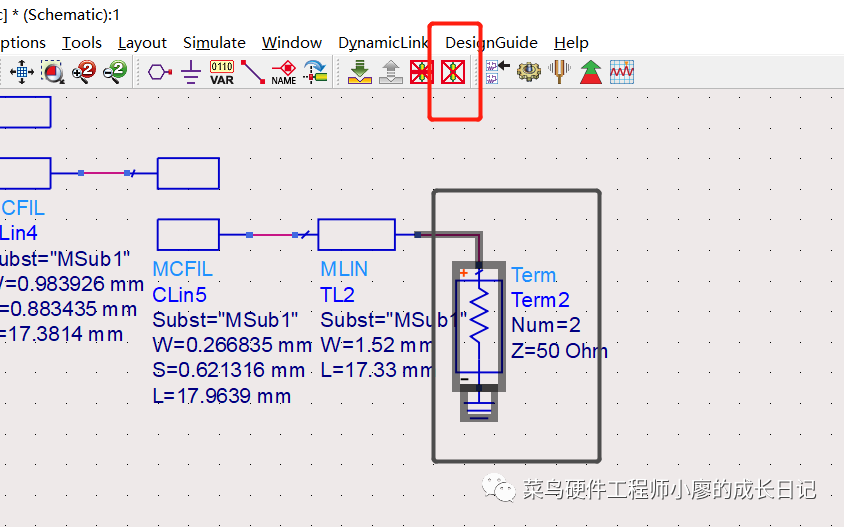

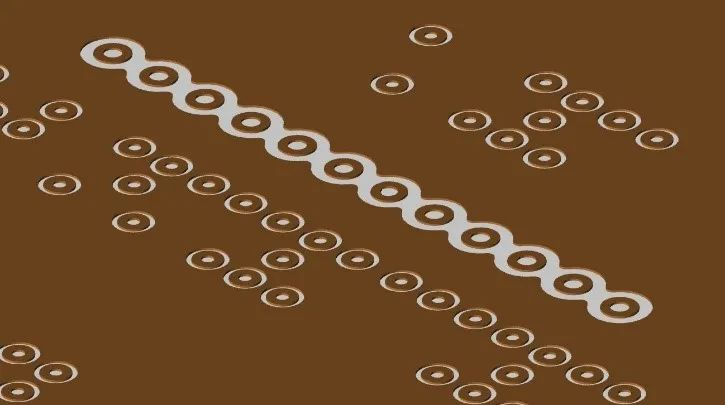

完成滤波器的原理图后,还需要对滤波器生成版图进一步的仿真验证。首先对滤波器生产版图,之后再对版图进行仿真验证。

2023-06-30 10:38

在做射频链路电路仿真时,除了需要搭建原理图的器件模型电路,设计者还需要考虑到实际版图结构中传输线、过孔所带来的阻抗不连续性和串扰,以及介质材料的损耗特性带来的影响。因此,在前期建模过程中需要加入版图的结构,来模拟实际版图

2022-09-21 09:14

。要想做到这一点,可使用版图与原理图 (LVS) 对比流程来验证物理电路设计。LVS流程可阅读物理版图,提取出一个以SPICE电路表示法来描绘电气结构的网表。然后将这个提取

2018-06-05 11:49

版图验证工具不仅要支持扁平化验证,而且要支持层次化验证。扁平化验证是版图验证工具的基础;层次化验证充分利用版图层次,可以有效避免重复报错和提高处理版图的速度。对于大规模

2022-08-29 11:00

PCB 设计中的高速模拟版图设计技巧

2023-12-06 15:04

将ADS 版图文件EXPORT成GDSII stream Format 格式的mylayout.GDS文件,新建一个Project(工程文件),进入该文件的版图页面(New Layout Window)。

2011-08-08 14:48

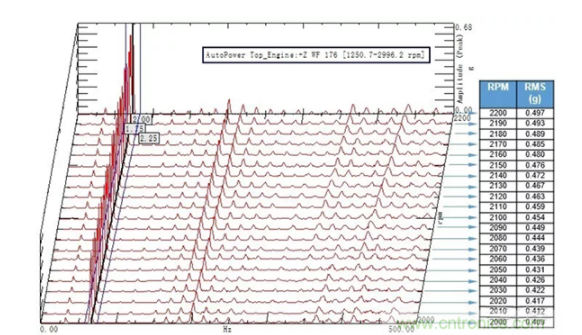

当需要比较各阶次的相对大小、对总量级OA的贡献,以及评价阶次的线性度时都需要对阶次进行提取。而常规提取出来的阶次是不带相位信息的,在这里我们讲一讲带相位的阶次提取、以及各种阶次

2021-04-04 16:08

将PCB原理图传递给版图(layout)设计时需要考虑的六件事。提到的所有例子都是用Multisim设计环境开发的,不过在使用不同的EDA工具时相同的概念同样适用哦!

2022-11-09 16:44