介绍了芯片流片的原理同时介绍了首颗极大规模全异步电路芯片流片成功。

2023-11-30 10:30

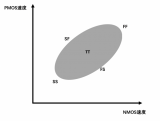

芯片制造是一个物理过程,存在着工艺偏差(包括掺杂浓度、扩散深度、刻蚀程度等),导致不同批次之间,同一批次不同晶圆之间,同一晶圆不同芯片之间情况都是不相同的。在一片wafer上,不可能每点的载流子平均

2023-12-01 13:31

foundry把MIM层做错了。反复强调MIM不做在M6和M5之间,做在M4和M3之间。芯片回来各种测试,codec就是不工作。经过多次质疑foundry,终于发现是没按照要求做。耽误半年。

2023-05-25 11:40

ASIC的复杂性不断提高,同时工艺在不断地改进,如何在较短的时间内开发一个稳定的可重用的ASIC芯片的设计,并且一次性流片成功,这需要一个成熟的ASIC的设计方法和开发流程。

2016-12-12 14:07

我们很高兴能在此宣布,Cadence 基于 UCIe 标准封装 IP 已在 Samsung Foundry 的 5nm 汽车工艺上实现首次流片成功。这一里程碑彰显了我们持续提供高性能车规级 IP 解决方案的承诺,可满足新一代汽车电子和高性能计算应用的严格要求。

2025-04-16 10:17

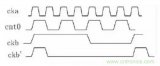

本文结合NCverilog,DesignCompile,Astro等ASIC设计所用到的EDA软件,从工艺独立性、系统的稳定性、复杂性的角度对比各种ASIC的设计方法,介绍了在编码设计、综合设计、静态时序分析和时序仿真等阶段经常忽视的问题以及避免的办法,从而使得整个设计具有可控性。

2016-11-29 01:04

芯片在研发过程中一般包含4个阶段:芯片设计、生产样片、测试验证和大规模量产。在完成芯片设计后,工程师们需要先拿到一些芯片样片,用它们进行测试和验证,来判断新研发的芯片在功能和性能上是否符合设计要求。如果样片通过测试,就可以按计划进行量产、商用;如果样片存在设计缺陷,则需要修改芯片设计,再次生产样片进行测试。

2025-09-09 15:04

半导体厂商如何做芯片的出厂测试呢,这对芯片来说,是流片后或者上市前的必须环节。

2016-06-18 15:56