MP3常见问题汇集 硬件篇 1.几款主要MP3的主芯片是什么?其特点是什么? IRIVER IFP

2010-02-02 13:44

ORCAD使用中常见问题汇集及答案 1、什么时FANOUT布线?FANOUT布线:延伸焊盘式布线。为了保证SMD器件的贴装质量,一般遵循在SMD焊盘上不打孔的原则,因此用f

2009-07-02 22:00

阻抗匹配及相关知识汇集 阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反

2010-01-23 11:18

圆形焊盘——广泛用于元件规则排列的单

2010-06-13 17:26

您必须掌握的电脑病毒知识汇集 1.经常死机:病毒打开了许多文件或占用了大量内存;不稳定(如内存质量差,硬件超频性能差

2010-02-11 15:12

将ASIC设计移植到FPGA芯片中,对于大部分设计团队来讲都是巨大的挑战。主要体现在:ASIC的设计一般都非常大,往往需要做多FPGA芯片划分;需要支持足够的处理性能;需要保证其功能的正确性;需要保证移植前后的功能具有等价性。

2022-04-14 15:01

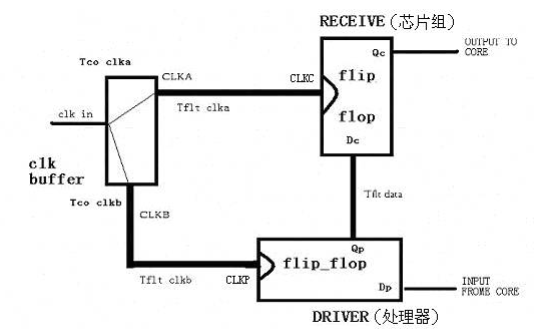

对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。因此,对于一个信号完整性工程师来说,如果不懂得系统时序的理论,那肯定是不称职的。本章我们就普通时序(共同时钟)和源同步系统时序等方面对系统时序的基础知识作一些简单的介绍。

2022-12-13 10:50

上式中:Tco_clkb是系统时钟信号CLKB在时钟驱动器的内部延迟;Tflt_ clkb 是CLKB从时钟驱动器输出后到达发送端(CPU)触发器的飞行时间;Tco_data是数据在发送端的内部延迟;Tflt_data是数据从发送端输出到接收端的飞行时间。

2022-12-21 15:43

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。下面我们来看看这种源同步时钟系统的结构。

2022-12-26 17:04

集博科技推出连网型数据汇集终端机的方案 客户现有生产线的数据汇集是于每个生产在线设置计算机,再外加串行通信卡以连接在线不同的数据汇集设备,如RFID接受器

2009-12-31 08:36