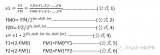

(1) 标号: BCDA 功能:多字节BCD码加法 给大家介绍一个单片机汇编语言写的多字节BCD码加法减法子程序 入口条件:字节数在R7中,被加数在[R0]中,加数在[

2020-12-06 17:31

单片机中的除法也是二进制的除法,和现实中数学的除法类似,是从被除数的高位开始,按位对除数进行相处取余的运算,得出的余数再和之后的被除数一起再进行新的相除取余的运算,直到除不尽为止,因为单片机中的

2018-05-31 08:51

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想

2023-07-04 10:03

在使用单片机中,unsigned int 占2个字节,unsigned char 占一个字节。而单片机是实行的字节寻址。16字节的bit寻址实在是不好用.

2019-09-07 10:17

除法器是电子技术领域的基础模块,在电子电路设计中得到广泛应用。目前,实现除法器的方法有硬件实现和软件实现两种方法。硬件

2012-05-24 09:41

乘除法很消耗CPU资源,查看汇编代码会发现,一个乘除法运算会编译出10几甚至几10行代码。如果是乘以或除以2的n次方,可以用>来实现,这种移位运算在编译时就已经算好了,

2018-06-26 16:36

模拟除法器是一种能实现两个模拟量相除的电子器件。目前不仅应用于模拟运算方面,而且已扩展到无线通讯、电视广播、人工神经网路、机器人控制技术等领域。此外,模拟除法器在模糊控制和测量仪表中也是非常重要的器件。

2014-09-19 15:14

通常无法在一个时钟周期内完成。因此FPGA实现除法运算并不是一个“/”号可以解决的。 好在此类基本运算均有免费的IP核使用,本人使用的VIVADO 2016.4开发环境提供的divider gen IP核均采用AXI总线接口,已经不再支持native接口。

2018-05-18 01:15

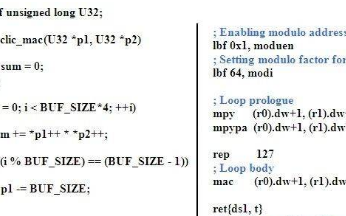

众所周知,汇编语言具有更高的性能优势,而用C语言编码则能更容易和快速地实现。DSP处理器功能的不断增强以及编译器优化技术的提高,使得传统的用汇编语言编写DSP应用程序的做法逐渐被淘汰。现在的DSP

2020-01-31 17:11

NI Multisim 10经典教程分享--除法与开平方运算电路

2023-02-08 09:18