比特流是一个常用词汇,用于描述包含FPGA完整内部配置状态的文件,包括布线、逻辑资源和IO设置。大多数现代FPGA都是基于SRAM的,包括Xilinx Spartan和Virtex系列。在FPGA上

2024-07-16 18:02

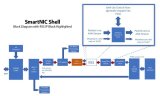

DVK是用于解码器IP设计和合规性验证的比特流和软件工具链。它是芯片RTL设计、目标设备集成(如智能手机、智能电视、机顶盒)、发货给客户前的软件堆栈验证的必备工具。

2022-10-08 11:06

背景: JTAG是英文“Joint Test Action Group(联合测试行为组织)”的词头字母的简写,该组织成立于1985 年,是由几家主要的电子制造商发起制订的PCB 和IC 测试标准。JTAG 建议于1990 年被IEEE 批准为IEEE1149.1-1990 测试访问端口和边界扫描结构标准。该标准规定了进行边界扫描所需要的硬件和软件。自从1990 年批准后,IEEE 分别于1993 年和1995 年对该标准作了补充,形成了现在使用的IEEE1149.1a-1993 和IEEE1149.1b-1994。

2018-06-29 13:09

编码器(encoder)是将信号(如比特流)或数据进行编制、转换为可用以通讯、传输和存储的信号形式的设备。

2020-11-18 17:26

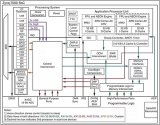

在使用 FPGA 构建的基于微控制器的典型系统中,开发人员需要管理用于加载 FPGA 编程比特流的序列和安全性。在 Zynq SoC 中,集成的处理器负责执行常规微控制器的任务,包括管理 PL 结构

2019-04-30 16:42

编码器(encoder)是将信号(如比特流)或数据进行编制、转换为可用以通讯、传输和存储的信号形式的设备。

2018-08-02 08:24

典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2022-03-14 14:02

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的 "代价"。但是这总是真的吗?

2023-06-27 10:10

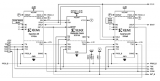

Δ-Σ ADC由Δ-Σ调制器和数字滤波器构成。调制器将模拟输入转换为数字比特流,而数字滤波器将比特流转换为表示模拟输入幅度的数据字。

2018-07-10 16:55

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程

2017-02-11 16:36