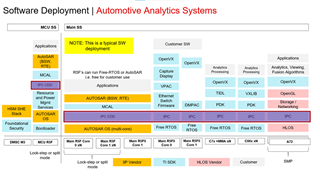

目前很多芯片都会有几个core核,有的是Cortex M0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核

2023-08-11 10:51

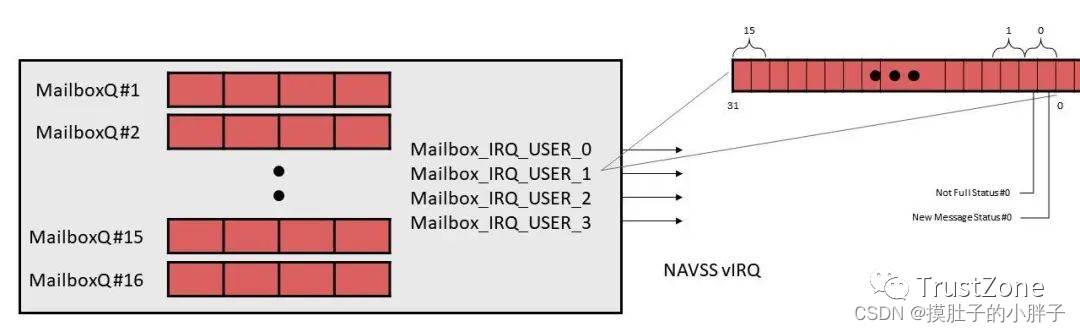

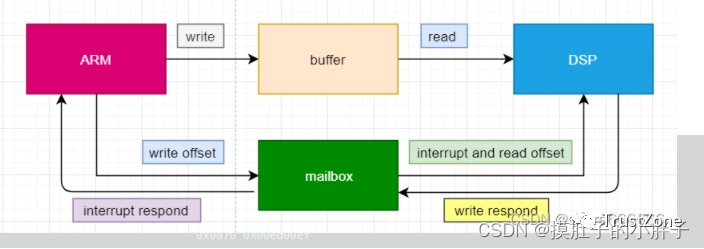

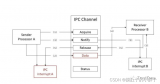

连接 4 个通信用户或 CPU。 J721E SoC 有 12 个硬件邮箱实例。即 12x 16 个硬件邮箱队列。 (硬件邮箱的逻辑框图) Mailbox and VRING 邮箱本质上充当一个非常

2023-09-13 17:35

基于FPGA的嵌入式应用在近几年来作为一个比较新颖的课题,本文在研究各种核间通信机制的基础上,提出了一种基于Mailbox核

2017-11-22 17:31

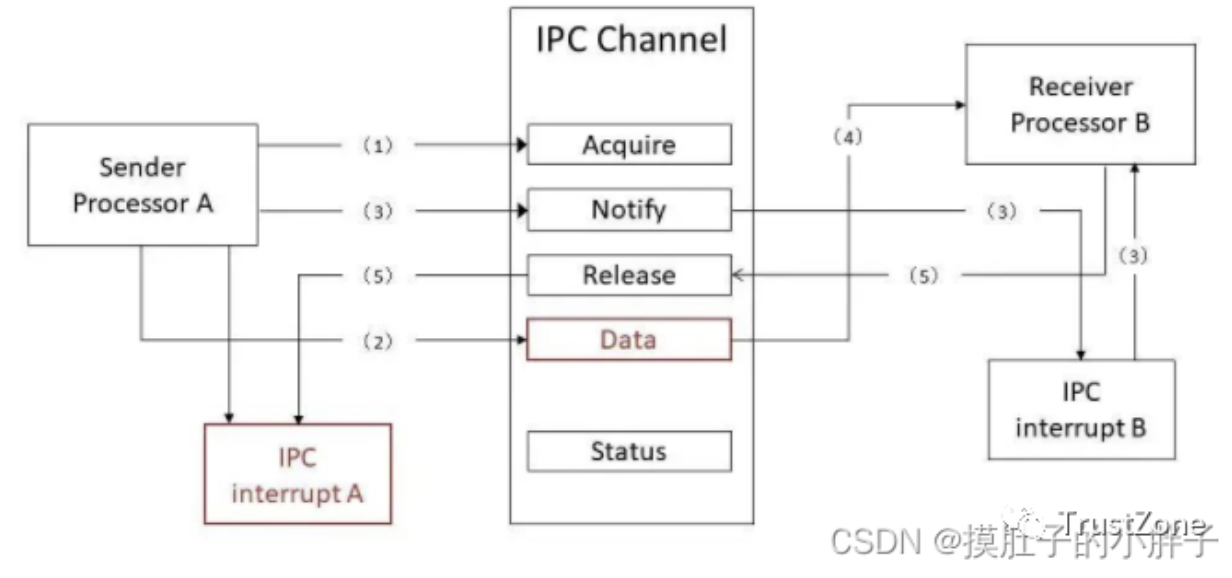

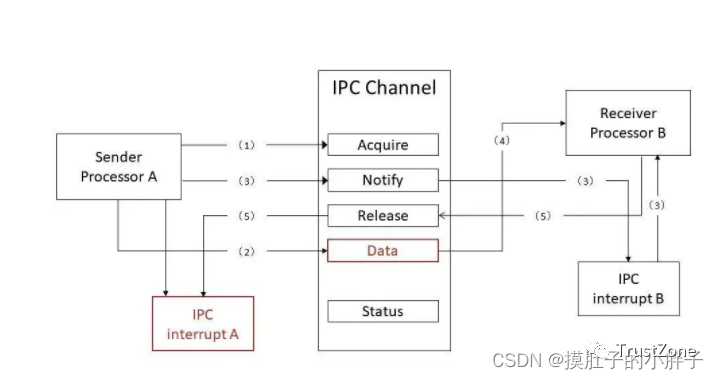

(Inter-processor communication)来核间通信,进行数据的交互。 核间

2023-09-13 17:32

理解为软件可自由定义的中断模块。 用于在片上处理器之间通信的一种mailbox队列中断机制,mailbox队列中断机制允许软件通过一组寄存器和关联的中断设置和得到信息在二个处理之间建立

2023-09-13 17:39

(Inter-processor Communication)机制。核间通信的主要目标是,充分利用硬件提供的机制,实现高

2023-03-16 09:19

目前很多芯片都会有几个core核,有的是Cortex M0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核

2023-09-05 17:29

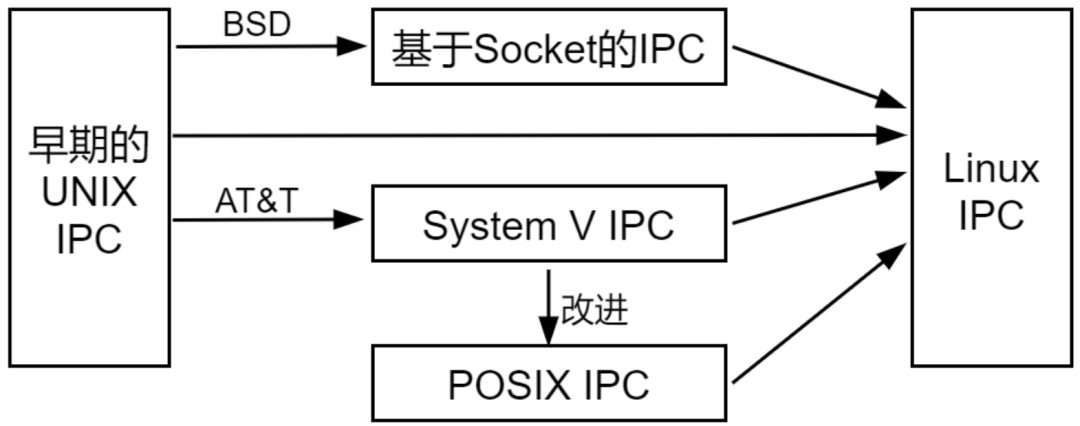

比较难,Linux内核提供了多种进程间通信的机制。 同一个进程的不同模块(譬如不同的函数)之间进行通信都是很简单的,譬如使用全局变量等。 通常情况下,大部分的程序是不要

2023-07-21 11:23

本文从对比两颗分立MCU与单芯片双核MCU开始(以LPC4350为例),展开介绍了非对称双核MCU的基础知识与重要特点。接下来,重点介绍了核间

2012-03-26 15:31

本文从对比两颗分立MCU与单芯片双核MCU开始(以LPC4350为例),展开介绍了非对称双核MCU的基础知识与重要特点。接下来,重点介绍了核间

2018-03-13 15:47