随着现代电子系统对高精度、高可靠性时钟信号需求的不断提升,时钟抖动成为影响系统性能的关键因素。核芯互联科技有限公司重磅推出CLF04828超低噪声去抖时钟,凭借其领先的双PLL架构、超低相位噪声和灵活的输出配置,为多

2025-03-04 12:38

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe

2023-06-08 15:29

在数据中心、人工智能和高性能计算需求爆发的今天,高速信号传输的稳定性和效率成为系统设计的核心挑战。核芯互联推出的CLRD320八通道redriver(线性转接驱动器)芯片,凭借多项技术创新,为

2025-03-14 11:44

核芯互联CL1656是一个16-bit、快速、低功耗逐次逼近型ADC,吞吐速率高达250 kSPS,并且内置低噪声、宽带宽采样保持放大器,完全P2P兼容AD7656,并且只需要5V单模拟电源供电(AD7656需要正负

2023-06-12 14:57

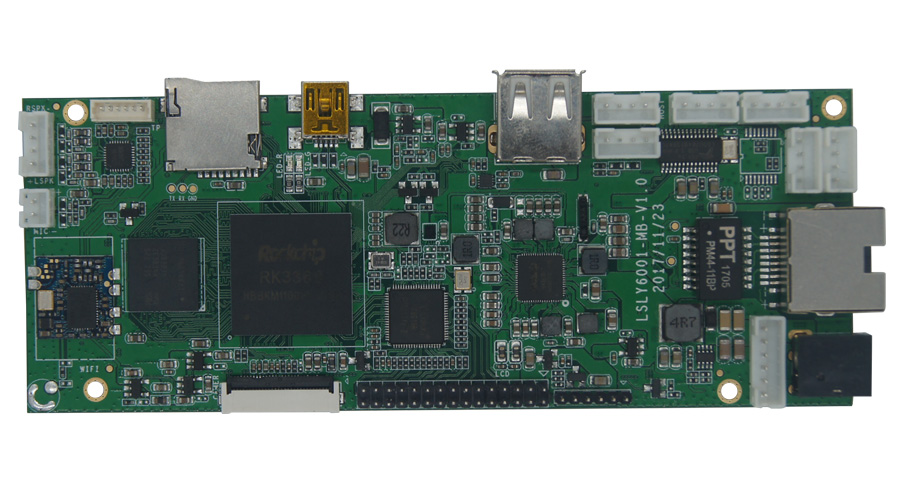

基于瑞芯微八核芯片 RK3368 方案,主频 1.5GHz。加强型电源管理电路,具备 WIFI、以太网,支持常用外接设备,接口丰富、性能稳定。

2019-10-14 17:11

目前域控项目有的采用S32G这类多核异构的芯片,转载一篇分析下多核异构中A核与M核通信过程的文章。

2023-10-31 11:09

双核双性能 多核不一定会使你的手机或电脑速度更快,但它将提高你的PC的整体性能,这是一个有所不同的细微的技术特色。多核处理器的性能提升并不是简单CPU核心的倍数,因为受到两(多)个核之间共享资源的拖累。比如双核性能只

2018-04-04 13:11

高斯滤波的卷积核确定主要依赖于高斯函数的特性以及图像处理的具体需求。以下是确定高斯滤波卷积核的几个关键步骤: 一、确定卷积核的大小 卷积核形状 :高斯滤波的卷积

2024-09-29 09:29

很多网友问处理器6核12线程和8核16线程的区别是什么,首先我们来了解下什么是6核12线程和8核16线程。

2022-01-01 17:44

在使用FPGA的时候,有些IP核是需要申请后才能使用的,本文介绍如何申请xilinx IP核的license。

2024-10-25 16:48