在现代电子电路设计中,晶振时钟信号的高频特性使得其容易受到各种干扰。其中,寄生电容、杂散电容和分布电容是影响晶振时钟信号稳定性的主要因素。晶发电子将详细分析这三种电容

2024-09-26 14:49

说到射频的难点不得不提杂散,杂散也是射频被称为“玄学”的来源。杂散也是学习射频必经的一个难点。本篇文章就来讲一下杂散。

2024-11-05 09:59

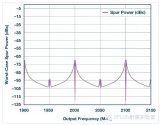

锁相环 (PLL) 和压控振荡器 (VCO) 输出特定频率的RF信号,理想情况下此信号应当是输出中的唯一信号。但事实上,输出中存在干扰杂散信号和相位噪声。本文讨论最麻烦的杂散信号之一——整数边界杂散,它如何仿真与消除

2023-05-22 11:10

。(2)电气判断法由于杂散电流难以直接测量,所以对于管道是否受到杂散电流影响,目前通常是按管地电位较自然电位正向偏移值来判断,如果管地电位较自然电位正向偏移值难以测量时

2020-12-01 16:22

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类

2023-08-21 18:20

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类

2023-09-04 16:29 Excelpoint世健 企业号

杂元件库。

2016-04-25 14:22

杂元件库----------------protel格式封装库

2016-03-11 17:50

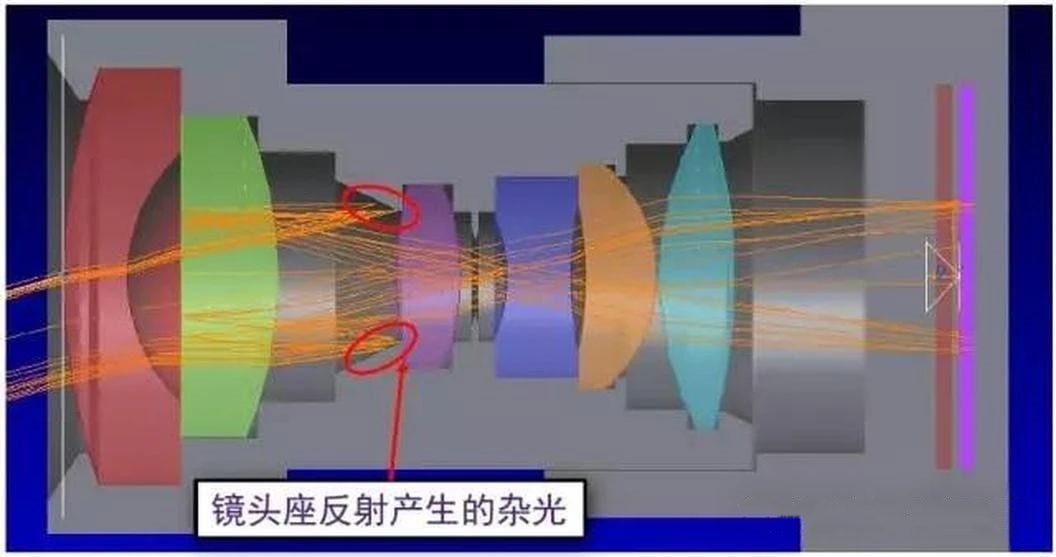

光学系统中的杂散光示意图(来自网络) 光学设计中的杂散光是从哪来的?在设计中“杂散光”概念的诠释和理解对于不同的光学设计者目前并不一致,导致设计者之间的交流受阻,在某种程度上阻碍了

2024-02-22 06:34

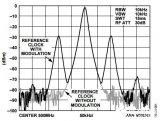

时钟:125M晶振给FPGA,FPGA分出120MHz给时钟buffer,时钟buffer将120M分发给AD9783作为参考时钟 FPGA发出的3M基带数据经DAC转换后输出波形如图,3M信号两边

2023-12-07 07:09